**The HVDC Options**

Jos Arrillaga Y. H. Liu N. R. Watson

The HVDC Options

J. Arrillaga University of Canterbury, New Zealand

> Y.H. Liu Inner Mongolia University, China

N.R. Watson University of Canterbury, New Zealand

John Wiley & Sons, Ltd

The HVDC Options

The HVDC Options

J. Arrillaga University of Canterbury, New Zealand

> Y.H. Liu Inner Mongolia University, China

N.R. Watson University of Canterbury, New Zealand

John Wiley & Sons, Ltd

Copyright © 2007

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England

Telephone (+44) 1243 779777

Email (for orders and customer service enquiries): cs-books@wiley.co.uk

Visit our Home Page on www.wiley.com

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP, UK, without the permission in writing of the Publisher. Requests to the Publisher should be addressed to the Permissions Department, John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England, or emailed to permreq@wiley.co.uk, or faxed to (+44) 1243 770620.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The Publisher is not associated with any product or vendor mentioned in this book.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

### Other Wiley Editorial Offices

John Wiley & Sons Inc., 111 River Street, Hoboken, NJ 07030, USA

Jossey-Bass, 989 Market Street, San Francisco, CA 94103-1741, USA

Wiley-VCH Verlag GmbH, Boschstr. 12, D-69469 Weinheim, Germany

John Wiley & Sons Australia Ltd, 42 McDougall Street, Milton, Queensland 4064, Australia

John Wiley & Sons (Asia) Pte Ltd, 2 Clementi Loop #02-01, Jin Xing Distripark, Singapore 129809

John Wiley & Sons Canada Ltd, 6045 Freemont Blvd, Mississauga, ONT, Canada L5R 4J3

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Anniversary Logo Design: Richard J. Pacifico

#### Library of Congress Cataloging in Publication Data

Arrillaga, J.

Flexible power transmission—the HVDC options/J. Arrillaga, Y.H. Liu, N.R. Watson.

p. cm.

ISBN 978-0-470-05688-2 (cloth)

1. Electric power transmission. 2. Electric power distribution. I. Liu, Y. H.

II. Watson, N. R. III. Title.

TK3111.A76 2007

621.319'12-dc22

2007019888

#### British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

ISBN 978-0-470-05688-2 (HB)

Typeset in 10/12pt Times by Integra Software Services Pvt. Ltd, Pondicherry, India

Printed and bound in Great Britain by Antony Rowe Ltd, Chippenham, Wiltshire

This book is printed on acid-free paper responsibly manufactured from sustainable forestry in which at least two trees are planted for each one used for paper production.

# **Contents**

| Pı | refac | e                                                                  | xi |

|----|-------|--------------------------------------------------------------------|----|

| 1  | Inti  | coduction                                                          | 1  |

|    | 1.1   | The Conventional Power Grid                                        | 1  |

|    |       | 1.1.1 Power Transfer Mechanism                                     | 1  |

|    | 1.2   | Towards a More Flexible Power Grid                                 | 5  |

|    |       | 1.2.1 Power Electronics Control                                    | 5  |

|    | 1.3   | HVDC Transmission                                                  | 8  |

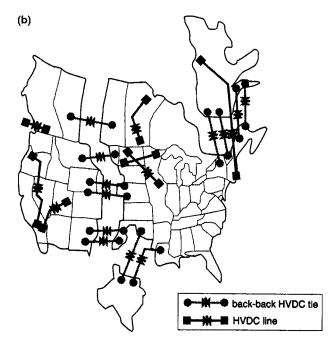

|    |       | 1.3.1 Thyristor-Based CSC Transmission                             | 10 |

|    |       | 1.3.2 VSC Transmission Based on the Integrated Gate Bipolar        |    |

|    |       | Transistor (IGBT)                                                  | 11 |

|    |       | 1.3.3 Multi-terminal HVDC                                          | 12 |

|    |       | 1.3.4 The Flexibility Concept Applied to HVDC                      | 13 |

|    | 1.4   | Relative Power Carrying Capability of AC and DC Transmission Lines | 13 |

|    | 1.5   | The Impact of Distributed Generation                               | 16 |

|    | 1.6   | The Effect of Electricity Deregulation                             | 16 |

|    | 1.7   | Discussion                                                         | 18 |

|    | Refe  | erences                                                            | 19 |

| 2  | Sen   | niconductor Power Devices                                          | 21 |

|    | 2.1   | Introduction                                                       | 21 |

|    | 2.2   | Semiconductor Principles                                           | 21 |

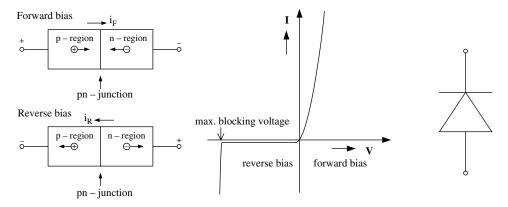

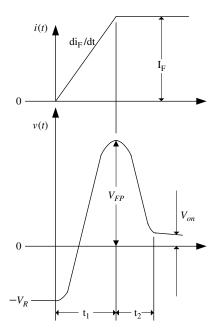

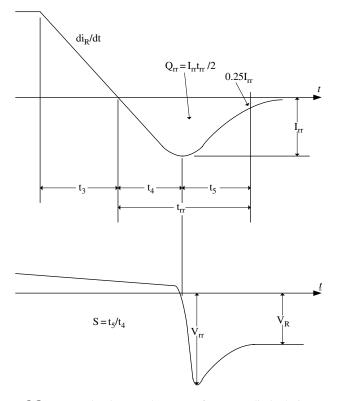

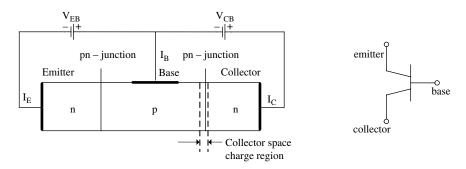

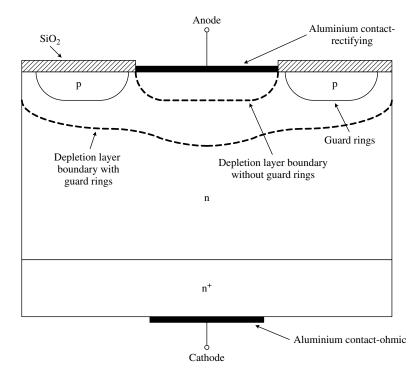

|    | 2.3   | Power Semiconductor Elements                                       | 22 |

|    |       | 2.3.1 The pn Rectifier                                             | 22 |

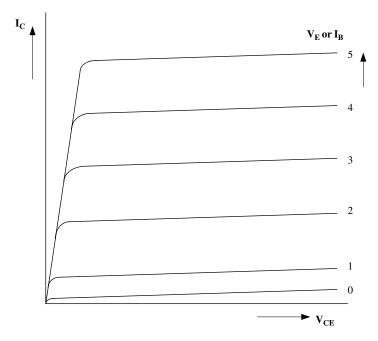

|    |       | 2.3.2 The Transistor                                               | 25 |

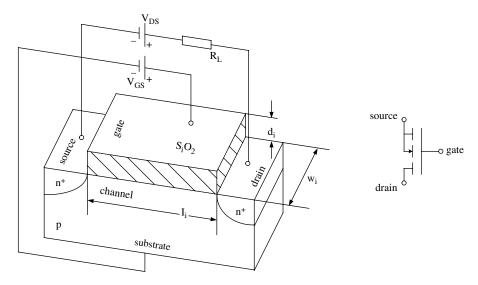

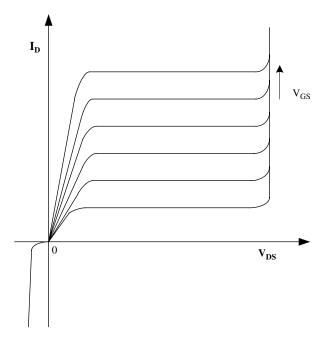

|    |       | 2.3.3 Metal-Oxide-Semiconductor Field-Effect                       |    |

|    |       | Transistor                                                         | 25 |

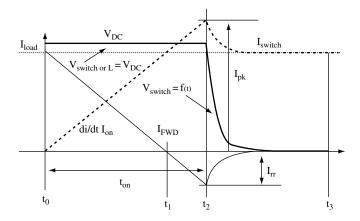

|    | 2.4   | Dynamic Stresses on Power Switches                                 | 27 |

|    |       | 2.4.1 Rate of Change of Voltage $(dv/dt)$                          | 27 |

|    |       | 2.4.2 Rate of Change of Current $(di/dt)$                          | 28 |

|    |       | 2.4.3 Balancing Problems in Series Chains                          | 28 |

vi CONTENTS

|   | 2.5   | Other Switching Issues                        | 29 |

|---|-------|-----------------------------------------------|----|

|   |       | 2.5.1 Switching Frequency                     | 29 |

|   |       | 2.5.2 Switching Losses                        | 29 |

|   |       | 2.5.3 Soft Switching                          | 29 |

|   |       | 2.5.4 Use of Snubbers                         | 30 |

|   | 2.6   | Thyristor-Type Power Switches                 | 31 |

|   |       | 2.6.1 The Thyristor                           | 31 |

|   |       | 2.6.2 Gate Turn-Off Thyristor                 | 36 |

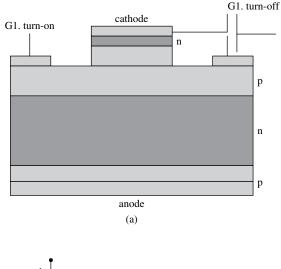

|   |       | 2.6.3 Insulated Gate-Commutated Thyristor     | 41 |

|   |       | 2.6.4 MOS Turn-Off Thyristor                  | 42 |

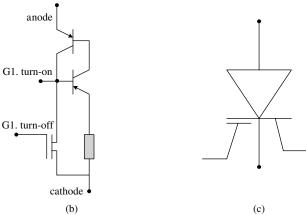

|   |       | 2.6.5 MOS Controlled Thyristor                | 44 |

|   |       | 2.6.6 Emitter Turn-Off Thyristor              | 45 |

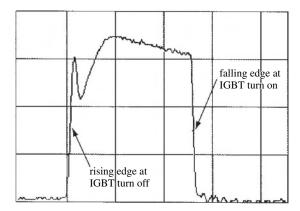

|   | 2.7   | Insulated Gate Bipolar Transistor             | 47 |

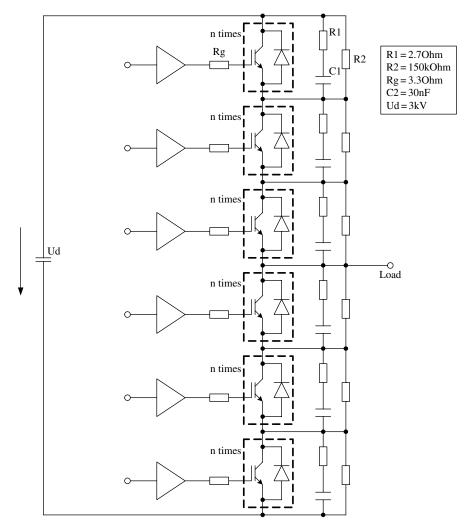

|   |       | 2.7.1 IGBT (Series) Chains                    | 49 |

|   | 2.8   | Diodes                                        | 51 |

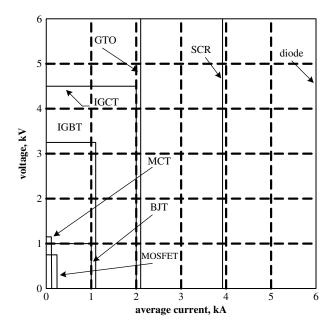

|   | 2.9   | Prognostic Assessment                         | 53 |

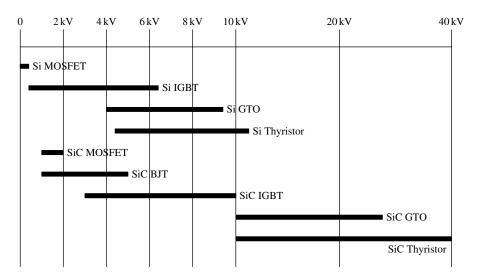

|   |       | 2.9.1 Ratings and Applicability               | 53 |

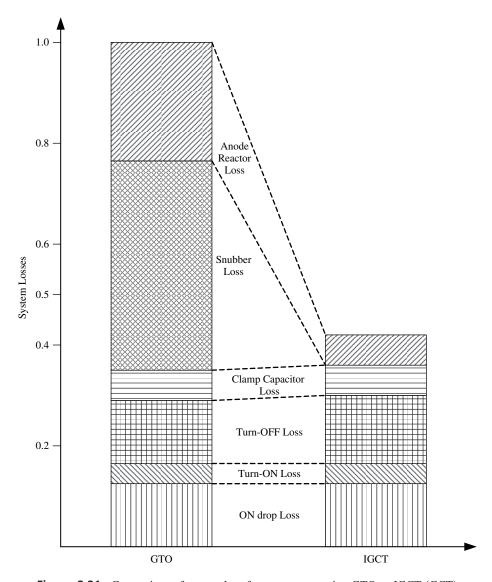

|   |       | 2.9.2 Relative Losses                         | 55 |

|   | Refer | rences                                        | 56 |

|   |       |                                               |    |

| _ |       |                                               |    |

| 3 |       | -Commutated HVDC Conversion                   | 57 |

|   | 3.1   | Introduction                                  | 57 |

|   | 3.2   | Three-Phase AC–DC Conversion                  | 57 |

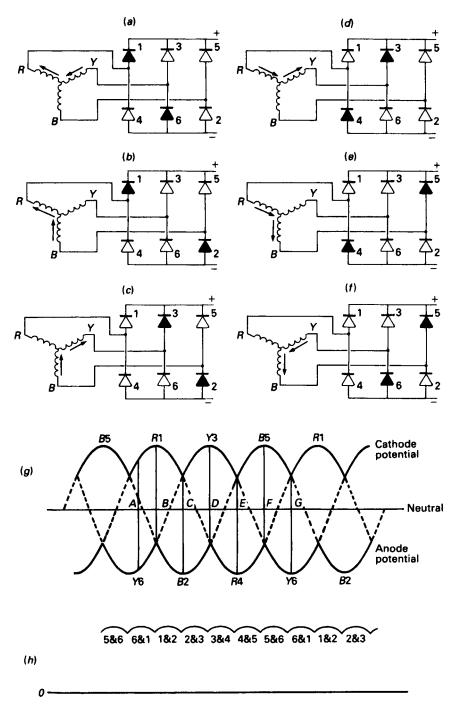

|   |       | 3.2.1 Basic CSC Operating Principles          | 58 |

|   | 2.2   | 3.2.2 Effect of Delaying the Firing Instant   | 58 |

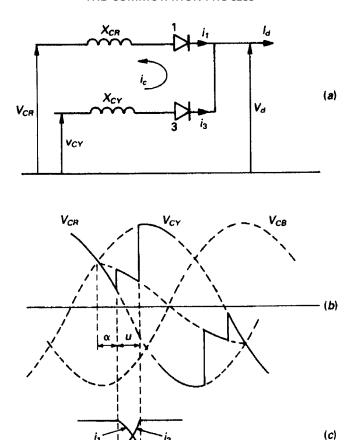

|   | 3.3   | The Commutation Process                       | 62 |

|   | 2.4   | 3.3.1 Analysis of the Commutation Circuit     | 62 |

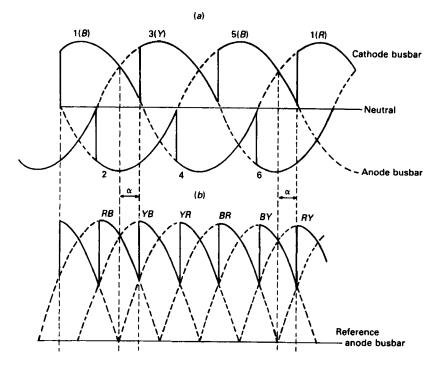

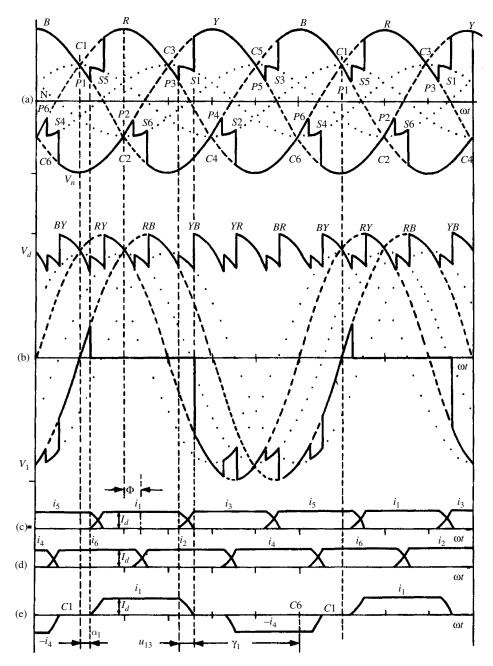

|   | 3.4   | Rectifier Operation                           | 64 |

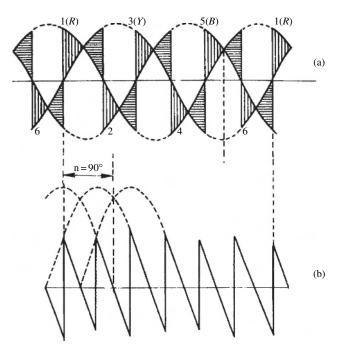

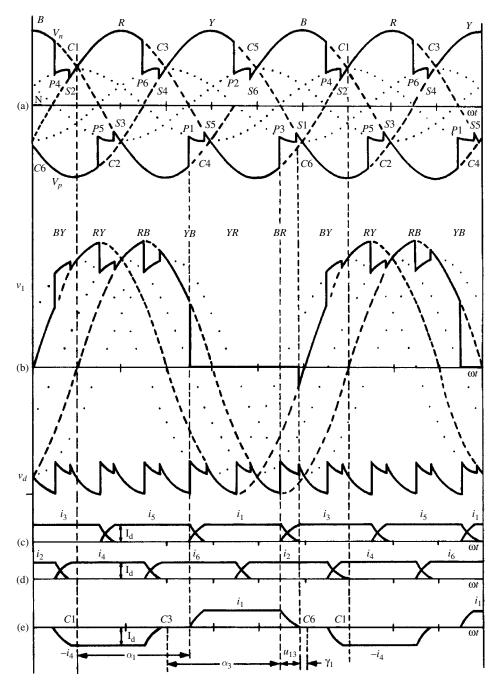

|   | 3.5   | Inverter Operation                            | 67 |

|   | 3.6   | Power Factor and Reactive Power               | 69 |

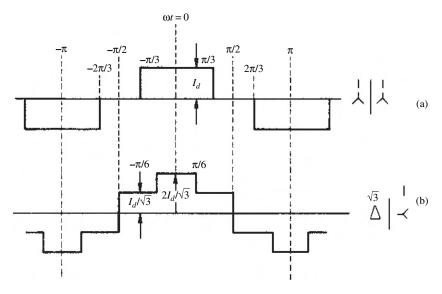

|   | 3.7   | Characteristic Harmonics                      | 71 |

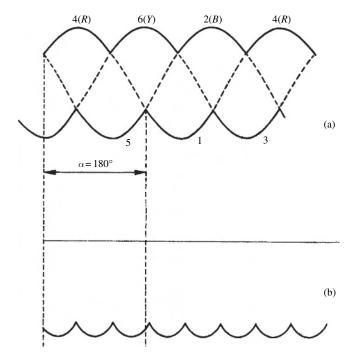

|   |       | 3.7.1 DC Side Harmonics                       | 72 |

|   | 2.0   | 3.7.2 AC Side Harmonics                       | 73 |

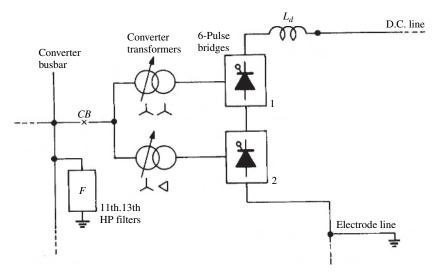

|   | 3.8   | Multi-Pulse Conversion                        | 74 |

|   |       | 3.8.1 Transformer Phase Shifting              | 74 |

|   | 2.0   | 3.8.2 DC Ripple Reinjection                   | 77 |

|   | 3.9   | Uncharacteristic Harmonics and Interharmonics | 81 |

|   |       | 3.9.1 Imperfect AC Source                     | 83 |

|   |       | 3.9.2 DC Modulation                           | 87 |

|   |       | 3.9.3 Control System Imperfections            | 88 |

|   |       | 3.9.4 Firing Asymmetry                        | 88 |

|   | 2.10  | 3.9.5 Magnification of Low-Order Harmonics    | 89 |

|   | 3.10  | Harmonic Reduction by Filters                 | 90 |

|   |       | 3.10.1 AC Side Filters                        | 90 |

|   |       | 3.10.2 DC Side Filters                        | 92 |

|   |      | CONTENTS                                                  | vii |

|---|------|-----------------------------------------------------------|-----|

|   | 3.11 | Frequency Cross-Modulation Across the LCC                 | 93  |

|   |      | Summary                                                   | 94  |

|   | Refe | erences                                                   | 94  |

| 4 | Self | -Commutating Conversion                                   | 97  |

|   | 4.1  | Introduction                                              | 97  |

|   | 4.2  | Voltage Source Conversion                                 | 97  |

|   |      | 4.2.1 VSC Operating Principles                            | 97  |

|   |      | 4.2.2 Converter Components                                | 102 |

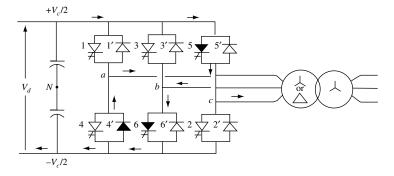

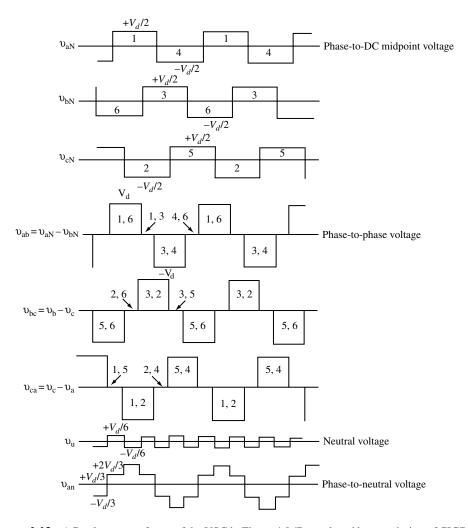

|   |      | 4.2.3 The Three-Phase VSC                                 | 105 |

|   | 4.3  | 1                                                         | 114 |

|   | 4.4  |                                                           | 114 |

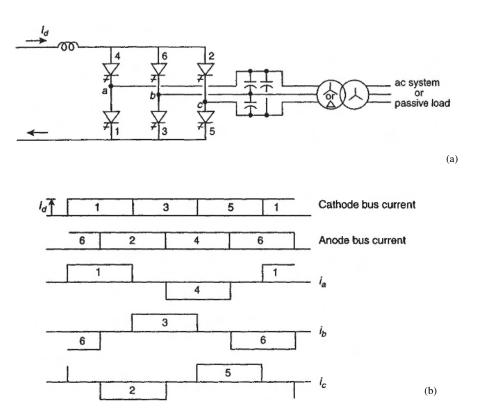

|   |      | 4.4.1 Analysis of the CSC Waveforms                       | 116 |

|   | 4.5  | 3                                                         | 116 |

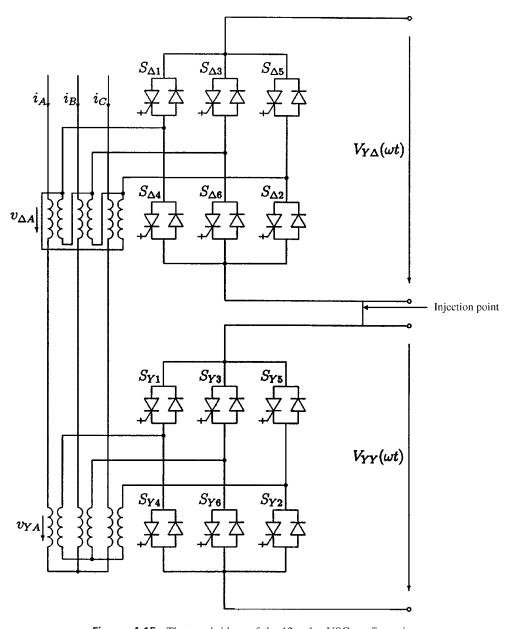

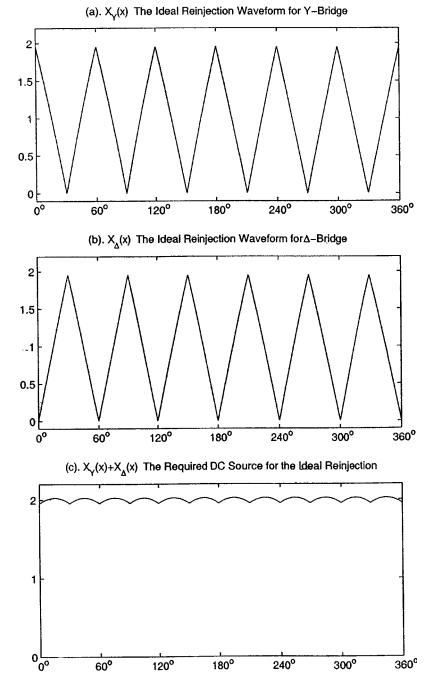

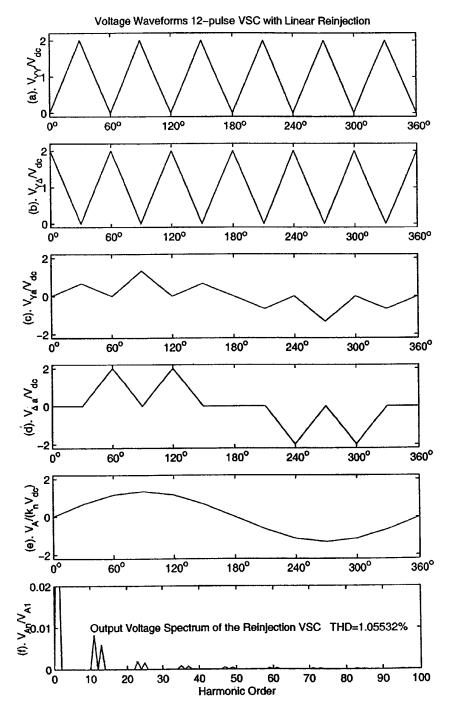

|   |      | 4.5.1 Application to VSC                                  | 116 |

|   |      | 4.5.2 Application to CSC                                  | 121 |

|   |      | Discussion                                                | 124 |

|   | Refe | erences                                                   | 125 |

| 5 | Puls | se Width Modulation                                       | 127 |

|   |      | Introduction                                              | 127 |

|   |      | PWM Operating Principles                                  | 127 |

|   |      | Selective Harmonic Cancellation                           | 128 |

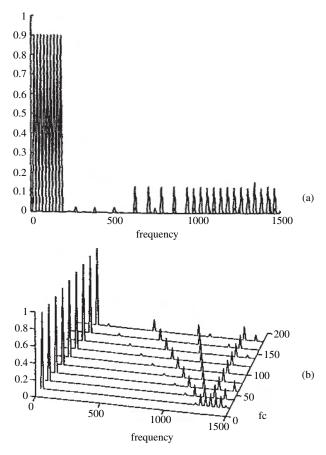

|   |      | Sinusoidal (Carrier-Based) PWM                            | 131 |

|   | 5.5  | PWM Carrier-Based Implementation                          | 133 |

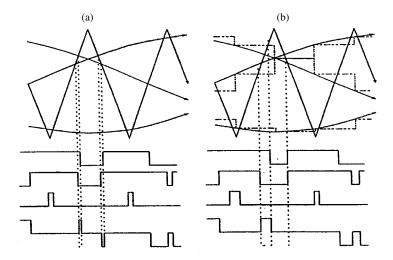

|   |      | 5.5.1 Naturally Sampled PWM                               | 134 |

|   |      | 5.5.2 Uniformly Sampled                                   | 136 |

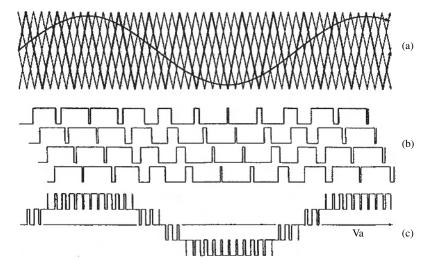

|   |      | Modulation in Multi-Bridge Converters                     | 137 |

|   | 5.7  | Summary                                                   | 138 |

|   | Refe | erences                                                   | 140 |

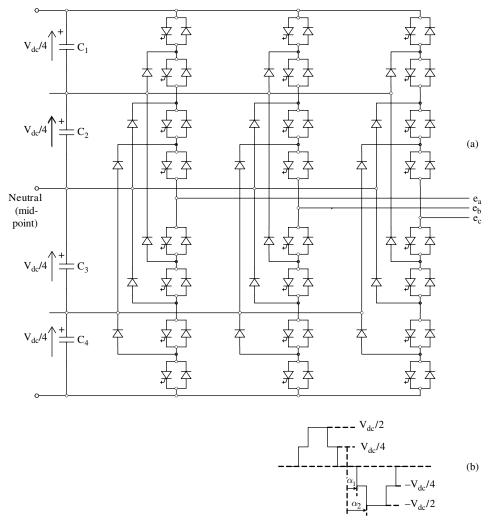

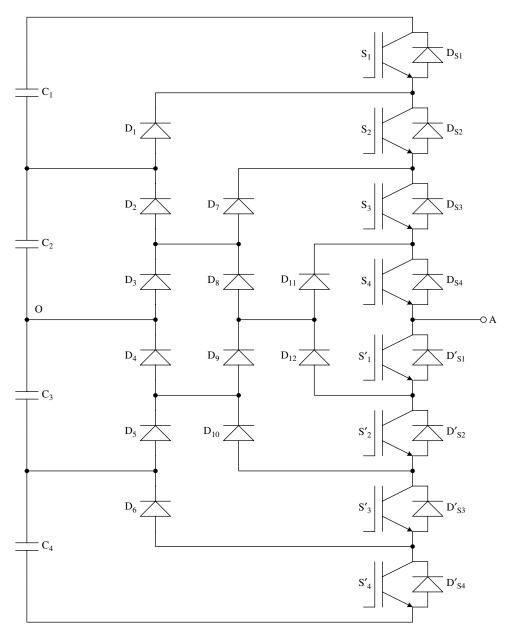

| 6 | Mu   | lti-Level Conversion                                      | 141 |

|   | 6.1  | Introduction                                              | 141 |

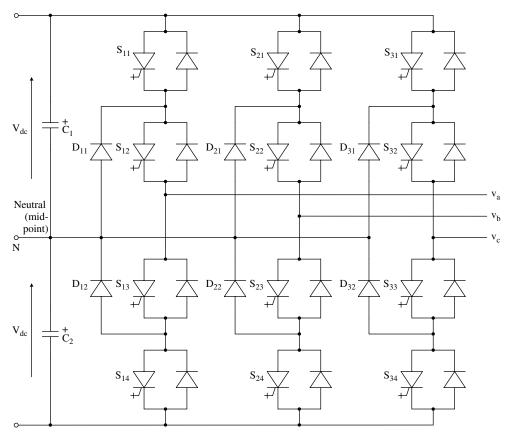

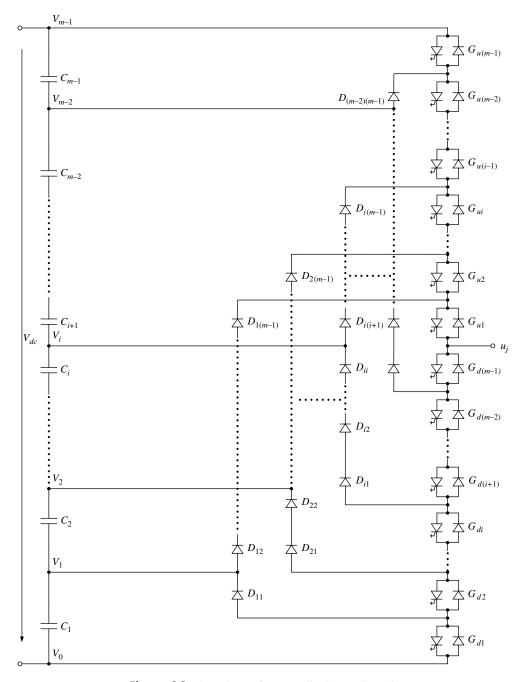

|   | 6.2  | Diode Clamping                                            | 142 |

|   |      | 6.2.1 Three-Level Neutral Point Clamped VSC               | 142 |

|   |      | 6.2.2 Five-Level Diode-Clamped VSC                        | 145 |

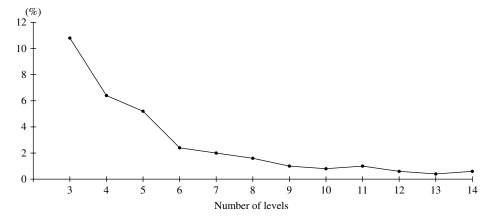

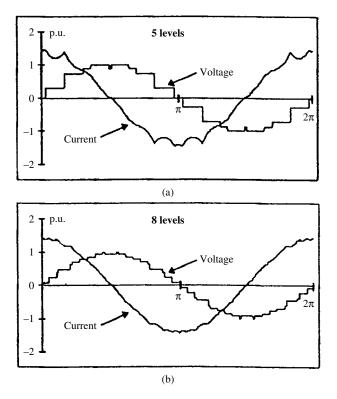

|   |      | 6.2.3 Diode Clamping Generalisation                       | 149 |

|   | 6.3  | Flying Capacitor Configuration                            | 154 |

|   |      | 6.3.1 Three-Level Flying Capacitor                        | 154 |

|   |      | 6.3.2 Multi-Level Flying Capacitor                        | 155 |

|   | 6.4  | Cascaded H-Bridge Configuration                           | 158 |

|   | 6.5  | Combined PWM/Multi-Level Conversion                       | 161 |

|   | 6.6  | Relative Merits of the Multi-Level Alternatives           | 164 |

|   |      | 6.6.1 A Cost Comparison of Alternative Configurations for | 1.7 |

|   |      | Use in HVDC                                               | 165 |

167

References

viii CONTENTS

| 7 | Mu                              | lti-Level DC Reinjection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 169                                                                                                                        |

|---|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   | 7.1                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 169                                                                                                                        |

|   | 7.2                             | Soft Switching in Multi-Level Reinjection Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 170                                                                                                                        |

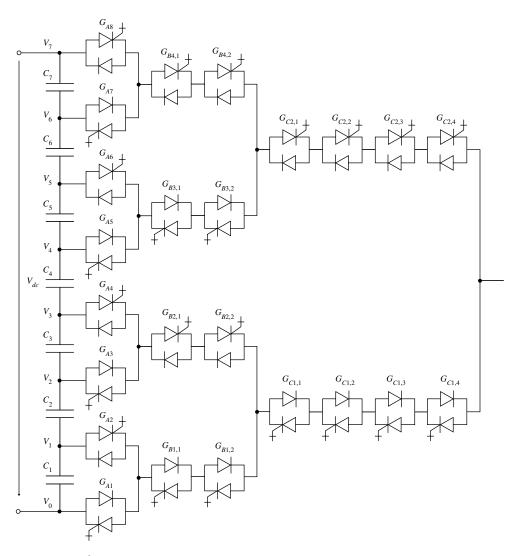

|   | 7.3                             | Clamp-Controlled MLVR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 170                                                                                                                        |

|   |                                 | 7.3.1 Firing Coordination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 174                                                                                                                        |

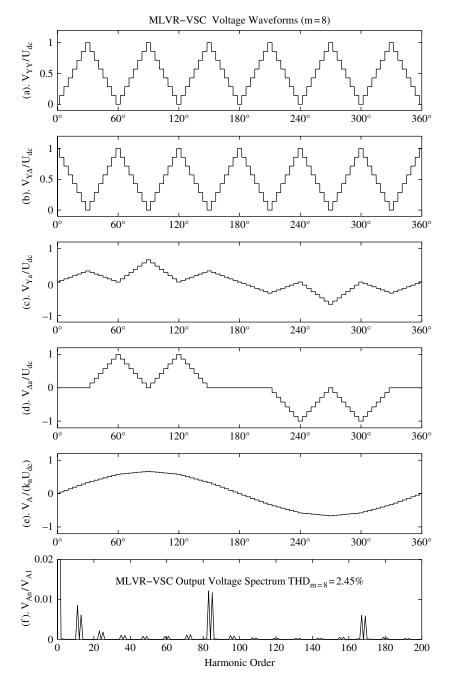

|   |                                 | 7.3.2 Analysis of the Voltage Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 176                                                                                                                        |

|   |                                 | 7.3.3 Analysis of the Output Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 178                                                                                                                        |

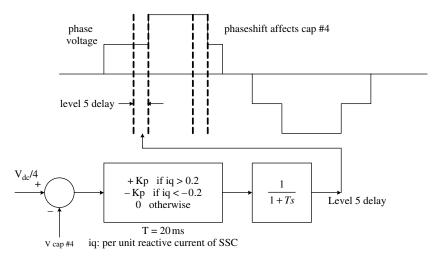

|   |                                 | 7.3.4 Capacitor Voltage Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 179                                                                                                                        |

|   |                                 | 7.3.5 Dynamic Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 185                                                                                                                        |

|   | 7.4                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 187                                                                                                                        |

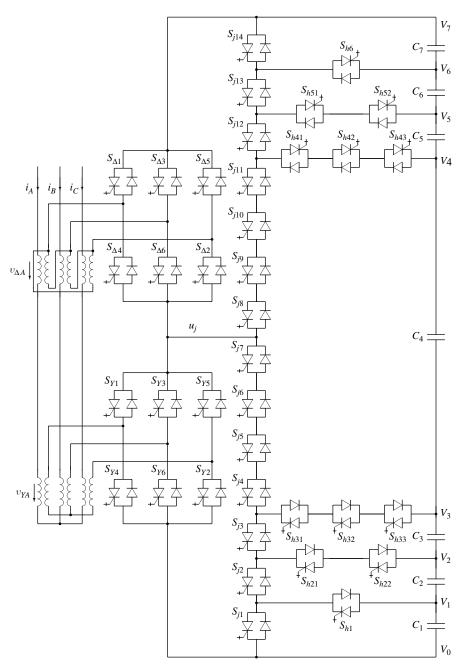

|   | 7.5                             | Cascaded H-Bridge MLVR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 193                                                                                                                        |

|   |                                 | 7.5.1 Basic Structure and Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 193                                                                                                                        |

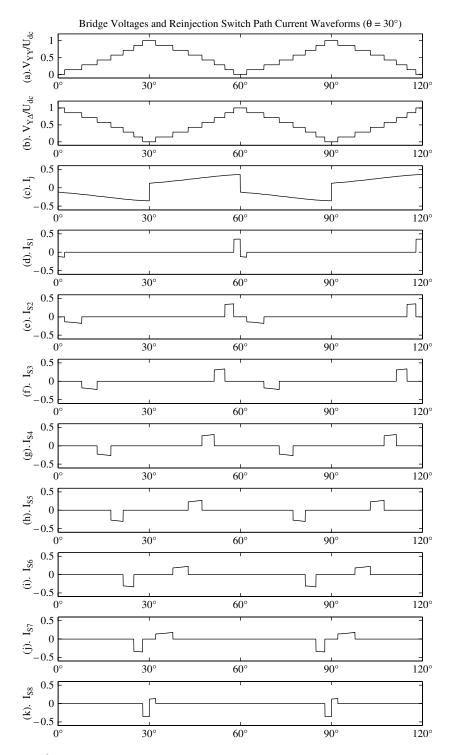

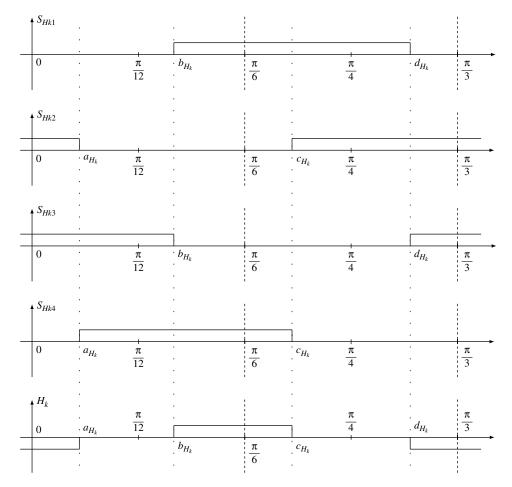

|   |                                 | 7.5.2 Switching Pattern of the Reinjection Bridges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 196                                                                                                                        |

|   |                                 | 7.5.3 Design of the Cascaded H-Bridge Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 197                                                                                                                        |

|   |                                 | 7.5.4 Capacitors' Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 199                                                                                                                        |

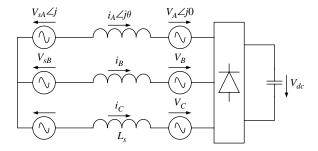

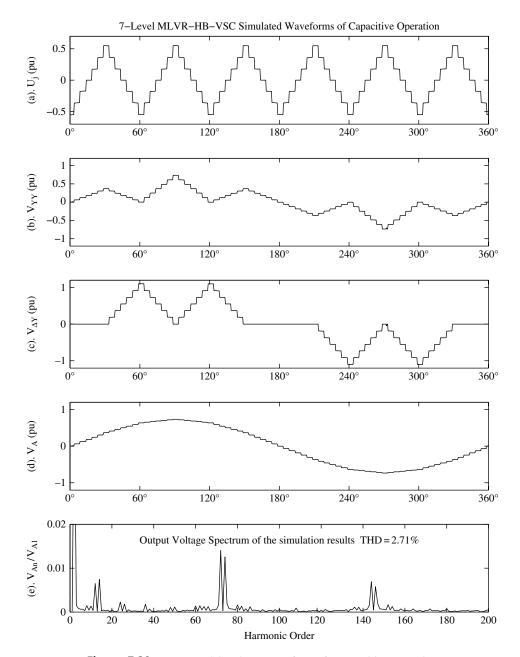

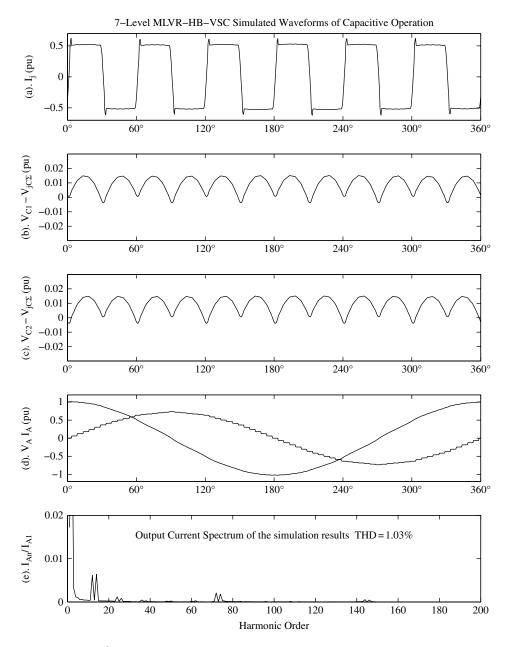

|   |                                 | 7.5.5 STATCOM Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 204                                                                                                                        |

|   | 7.6                             | **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 209                                                                                                                        |

|   | 7.7                             | Multi-Level Current Reinjection (MLCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 210                                                                                                                        |

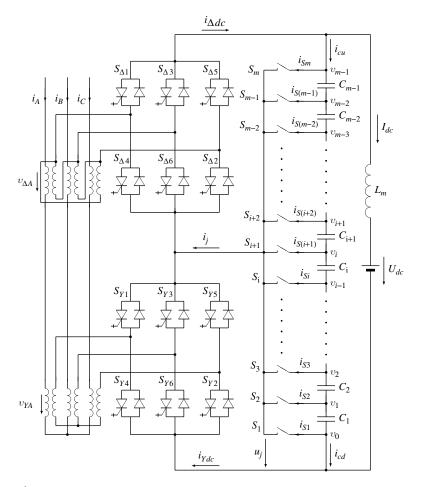

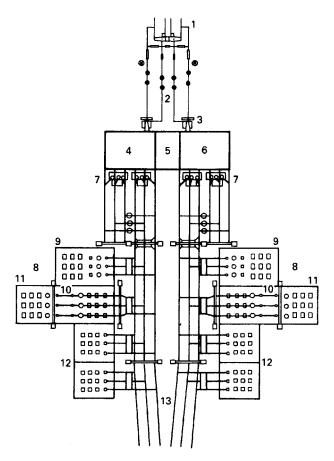

|   |                                 | 7.7.1 Structure and Operating Principles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 210                                                                                                                        |

|   |                                 | 7.7.2 Self-Commutating Thyristor Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 213                                                                                                                        |

|   |                                 | 7.7.3 EMTDC Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 216                                                                                                                        |

|   | 7.8                             | MLCR-CSC Versus MLVR-VSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 221                                                                                                                        |

|   | Refe                            | erences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 222                                                                                                                        |

| _ |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

| 8 |                                 | e-Commutated CSC Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 225                                                                                                                        |

|   | 0 1                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 225                                                                                                                        |

|   | 8.2                             | The Line-Commutated HVDC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 226                                                                                                                        |

|   | 8.2<br>8.3                      | The Line-Commutated HVDC Converter HVDC Converter Disturbances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 226<br>232                                                                                                                 |

|   | 8.2<br>8.3<br>8.4               | The Line-Commutated HVDC Converter<br>HVDC Converter Disturbances<br>Structure of the HVDC Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 226<br>232<br>233                                                                                                          |

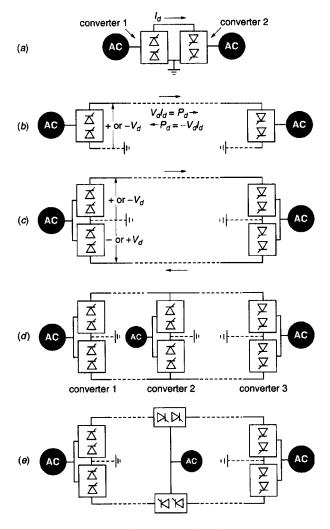

|   | 8.2<br>8.3<br>8.4<br>8.5        | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 226<br>232<br>233<br>239                                                                                                   |

|   | 8.2<br>8.3<br>8.4               | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 226<br>232<br>233<br>239<br>242                                                                                            |

|   | 8.2<br>8.3<br>8.4<br>8.5        | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 226<br>232<br>233<br>239<br>242<br>242                                                                                     |

|   | 8.2<br>8.3<br>8.4<br>8.5        | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels                                                                                                                                                                                                                                                                                                                                                                                                                                               | 226<br>232<br>233<br>239<br>242<br>242<br>243                                                                              |

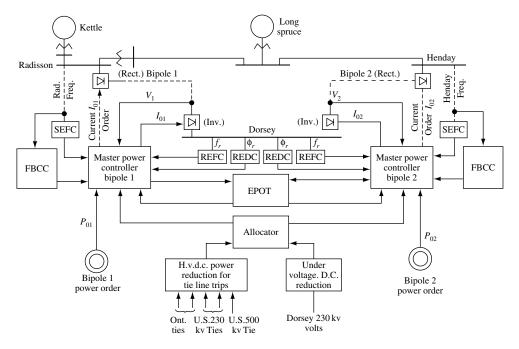

|   | 8.2<br>8.3<br>8.4<br>8.5        | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination                                                                                                                                                                                                                                                                                                                                                                                                            | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243                                                                       |

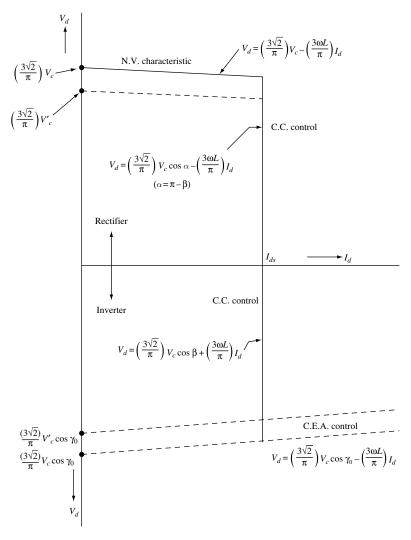

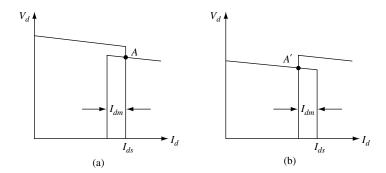

|   | 8.2<br>8.3<br>8.4<br>8.5        | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls                                                                                                                                                                                                                                                                                                                                                                                        | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245                                                                |

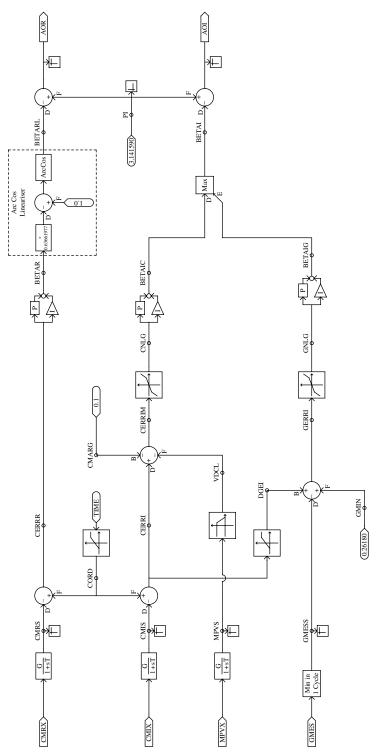

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls                                                                                                                                                                                                                                                                                                                                                          | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253                                                         |

|   | 8.2<br>8.3<br>8.4<br>8.5        | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction                                                                                                                                                                                                                                                                                                                                 | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253                                                         |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction                                                                                                                                                                                                                                                                                                       | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257                                                  |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation                                                                                                                                                                                                                                                                      | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258                                    |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems                                                                                                                                                                                                                            | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257                                                  |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected                                                                                                                                                                              | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259                             |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected Systems                                                                                                                                                                      | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259                             |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected Systems 8.7.5 Damping of Sub-Synchronous Resonances                                                                                                                          | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259                             |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected Systems 8.7.5 Damping of Sub-Synchronous Resonances 8.7.6 Active and Reactive Power Coordination                                                                             | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259                             |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected Systems 8.7.5 Damping of Sub-Synchronous Resonances 8.7.6 Active and Reactive Power Coordination 8.7.7 Transient Stabilisation of AC Systems                                 | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259<br>260<br>260<br>261<br>261 |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected Systems 8.7.5 Damping of Sub-Synchronous Resonances 8.7.6 Active and Reactive Power Coordination 8.7.7 Transient Stabilisation of AC Systems AC-DC-AC Frequency Interactions | 226<br>232<br>233<br>239<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259<br>260<br>260<br>261<br>261<br>262 |

|   | 8.2<br>8.3<br>8.4<br>8.5<br>8.6 | The Line-Commutated HVDC Converter HVDC Converter Disturbances Structure of the HVDC Link DC System Configurations DC System Control and Operation 8.6.1 General Philosophy 8.6.2 Different Control Levels 8.6.3 Overall Control Coordination 8.6.4 Pole Controls 8.6.5 Converter Unit Controls AC-DC System Interaction 8.7.1 Voltage Interaction 8.7.2 Dynamic Voltage Regulation 8.7.3 Dynamic Stabilisation of AC Systems 8.7.4 Controlled Damping of DC-Interconnected Systems 8.7.5 Damping of Sub-Synchronous Resonances 8.7.6 Active and Reactive Power Coordination 8.7.7 Transient Stabilisation of AC Systems                                 | 226<br>232<br>233<br>239<br>242<br>242<br>243<br>243<br>245<br>253<br>257<br>257<br>258<br>259<br>260<br>260<br>261<br>261 |

| i |

|---|

|   |

|    | 8.9  | DC Link Response to External Disturbances             | 266        |

|----|------|-------------------------------------------------------|------------|

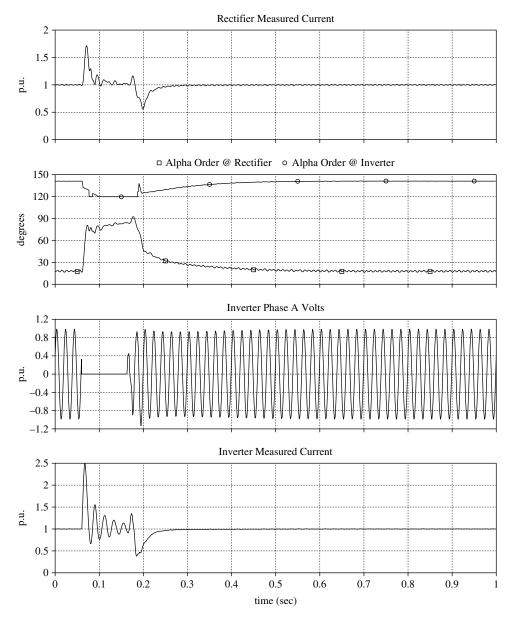

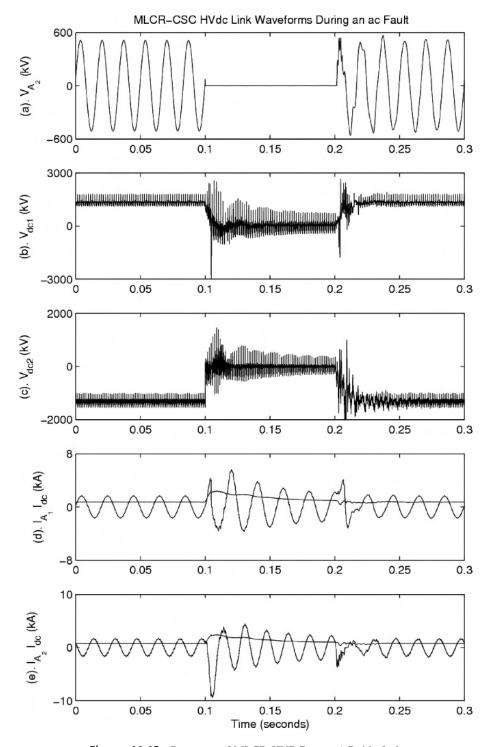

|    |      | 8.9.1 Response to AC System Faults                    | 266        |

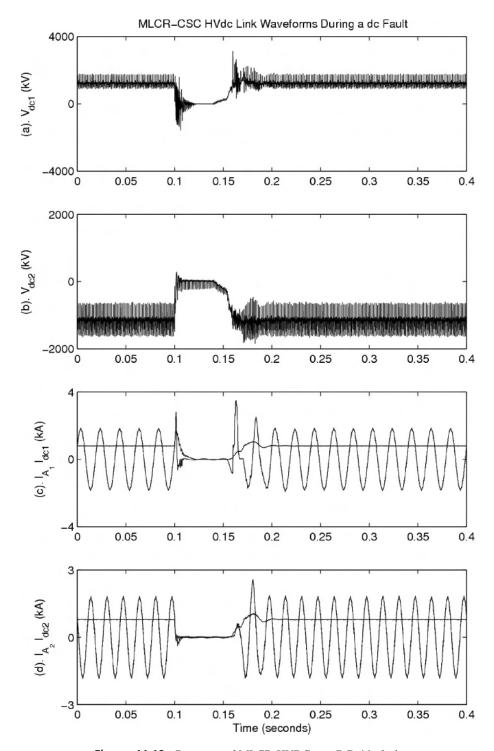

|    |      | 8.9.2 Response to DC Line Faults                      | 267        |

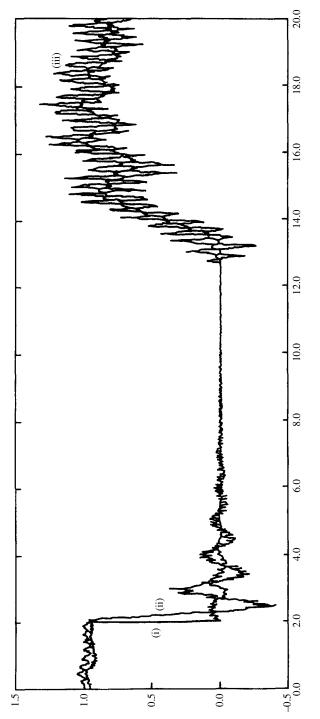

|    | 8.10 | Reliability of LCC Transmission                       | 267        |

|    | 8.11 | Concluding Statements                                 | 273        |

|    |      | rences                                                | 273        |

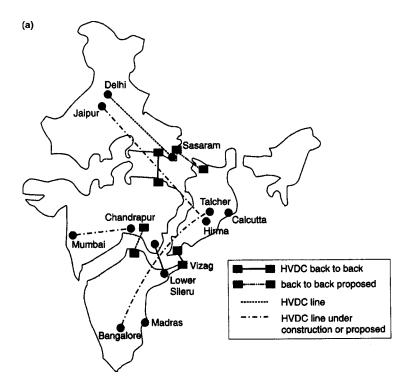

| 9  | Dev  | elopments in Line-Commutated HVDC Schemes             | 275        |

|    | 9.1  | Introduction                                          | 275<br>275 |

|    |      | Capacitor Commutated Conversion                       | 276        |

|    | 7.2  | 9.2.1 Basic CCC Operation                             | 277        |

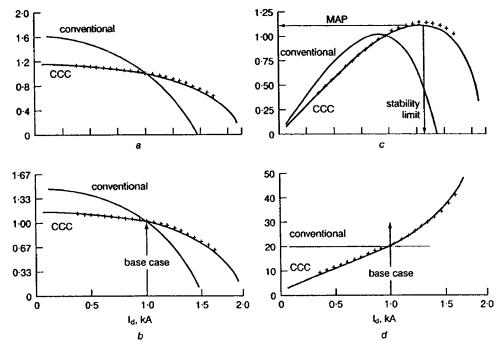

|    |      | 9.2.2 Simulated Performance                           | 277        |

|    | 9.3  | Continuously Tuned AC Filters                         | 280        |

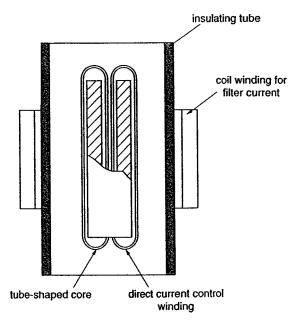

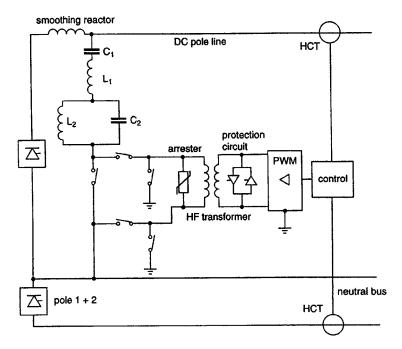

|    |      | Active DC Side Filters                                | 281        |

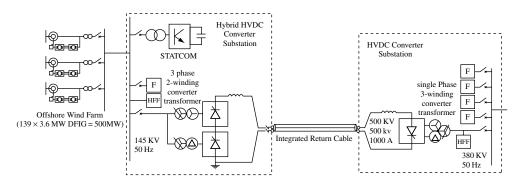

|    |      | STATCOM-Aided DC Transmission                         | 282        |

|    |      | AC Transmission Lines Converted for Use with HVDC     | 286        |

|    | ,.0  | 9.6.1 Modulated (Tripole) DC Transmission             | 287        |

|    | 9.7  | HVDC Transmission at Voltages above 600 kV            | 288        |

|    |      | Concluding Statements                                 | 289        |

|    |      | rences                                                | 289        |

| 10 | VSC  | CTransmission                                         | 291        |

| 10 |      | Introduction                                          | 291        |

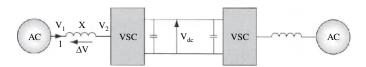

|    |      | Power Transfer Characteristics                        | 292        |

|    | 10.2 | 10.2.1 Current Relationships                          | 294        |

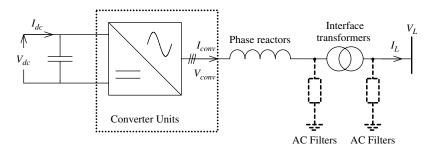

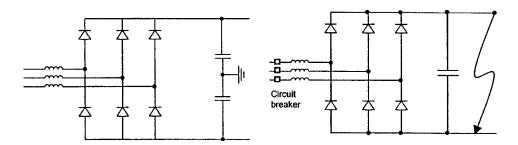

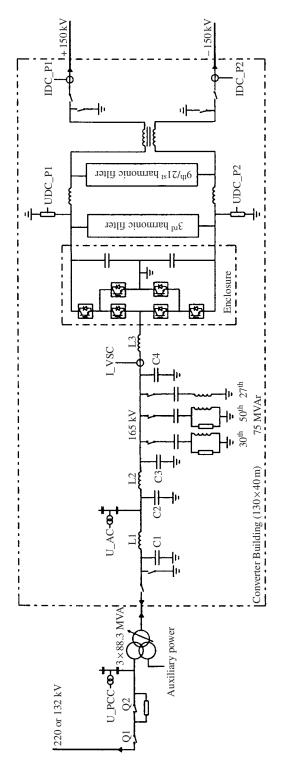

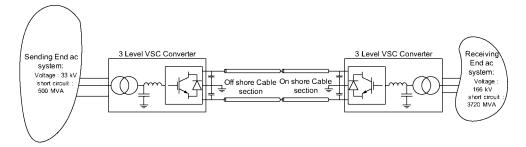

|    | 10.3 | Structure of the VSC Link                             | 296        |

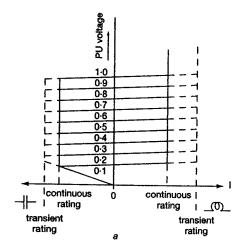

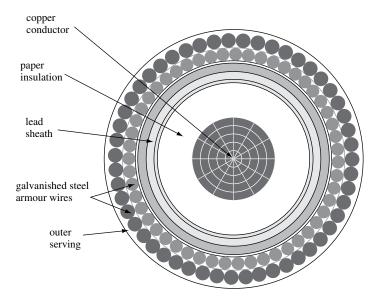

|    | 10.5 | 10.3.1 VSC-HVDC Cable Technology                      | 297<br>297 |

|    | 10.4 | VSC DC System Control                                 | 299        |

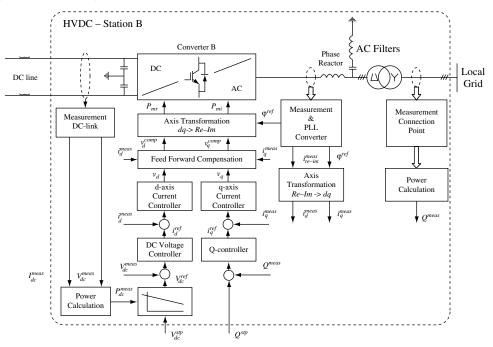

|    | 10.1 | 10.4.1 General Philosophy                             | 299        |

|    |      | 10.4.2 Different Control Levels                       | 302        |

|    |      | 10.4.3 DC Link Control Coordination                   | 303        |

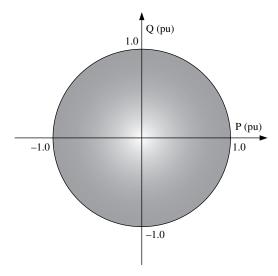

|    |      | 10.4.4 Control Capability of VSC Transmission         | 304        |

|    |      | 10.4.5 Assistance During Grid Restoration             | 305        |

|    | 10.5 | <u> </u>                                              | 306        |

|    |      | 10.5.1 Two-Level PWM Schemes                          | 308        |

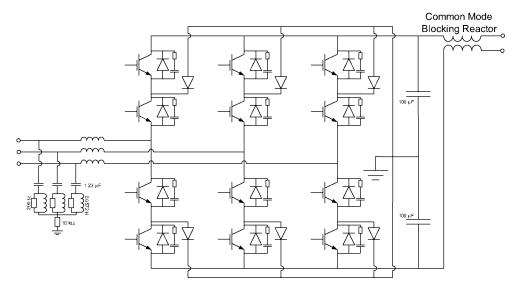

|    |      | 10.5.2 Three-Level PWM Schemes                        | 312        |

|    |      | 10.5.3 HVDC Light Performance                         | 314        |

|    | 10.6 | Other VSC Projects                                    | 321        |

|    |      | Potential for Multi-Terminal Sub-Transmission Systems | 323        |

|    |      | Discussion                                            | 324        |

|    | Refe | rences                                                | 326        |

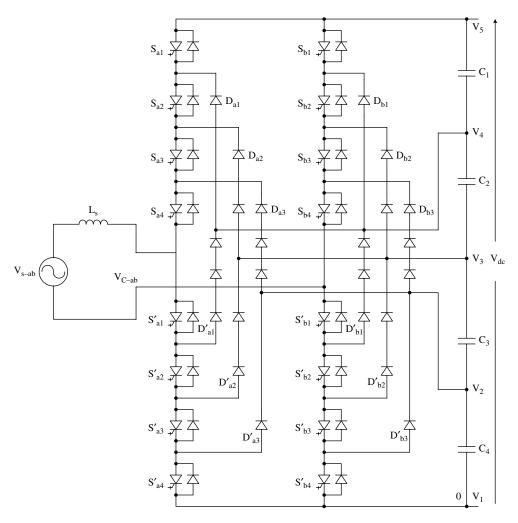

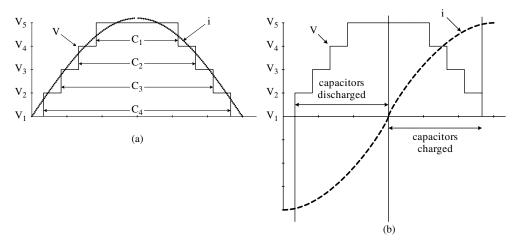

| 11 | Mul  | ti-Level VSC and CSC Transmission                     | 327        |

|    | 11.1 | Introduction                                          | 327        |

|    |      | Multi-Level VSC Transmission                          | 328        |

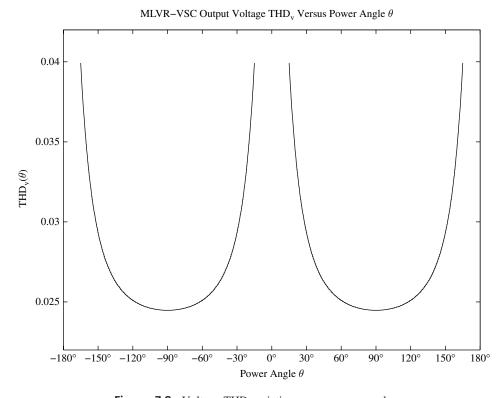

|    |      | 11.2.1 Power Flow Considerations                      | 328        |

|    |      | 11.2.2 DC Link Control Characteristics                | 331        |

|    |      |                                                       |            |

x CONTENTS

| Index |                                                                |     |

|-------|----------------------------------------------------------------|-----|

| Refe  | rences                                                         | 357 |

| 11.4  | Summary                                                        | 356 |

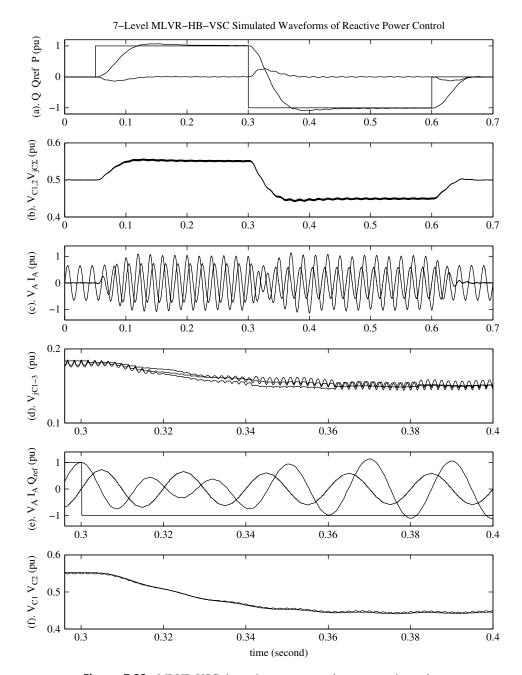

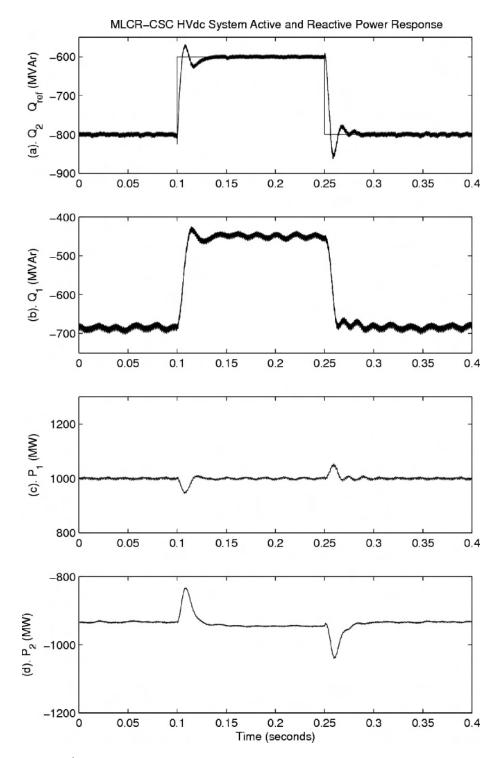

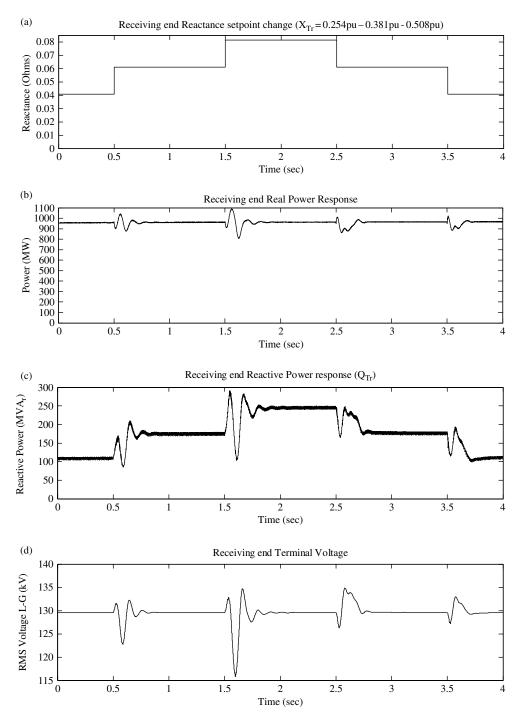

|       | 11.3.5 Reactive Power Control in Multi-Level CSC Transmission  | 352 |

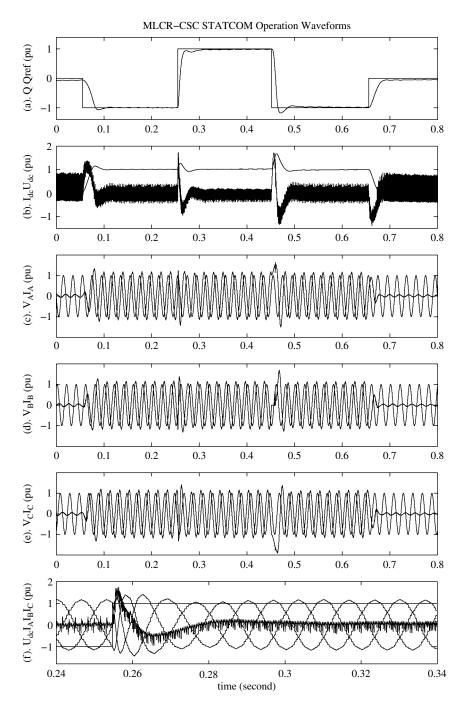

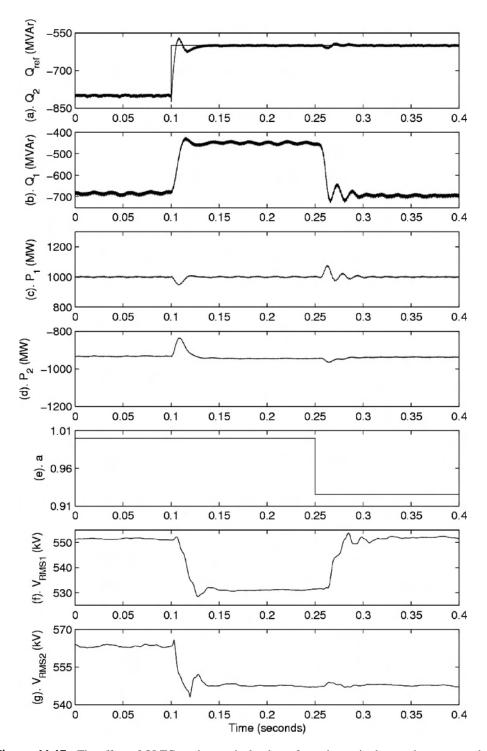

|       | 11.3.4 Simulated Performance Following Disturbances            | 348 |

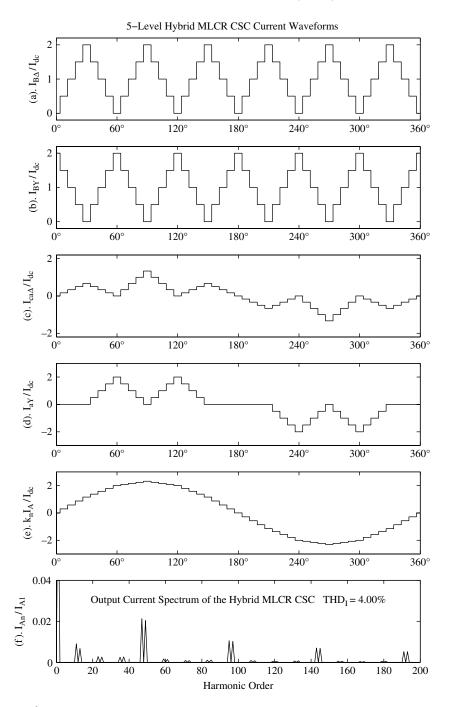

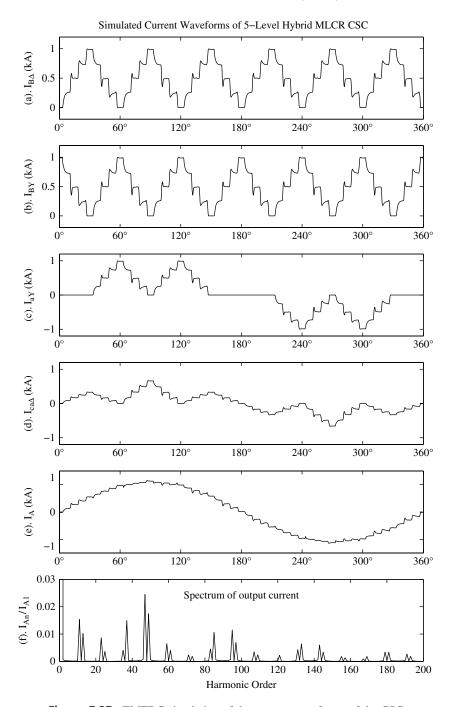

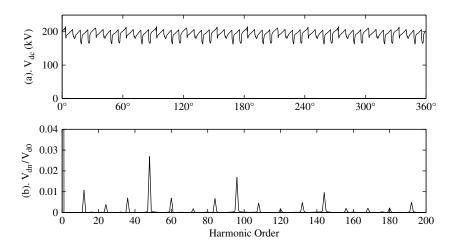

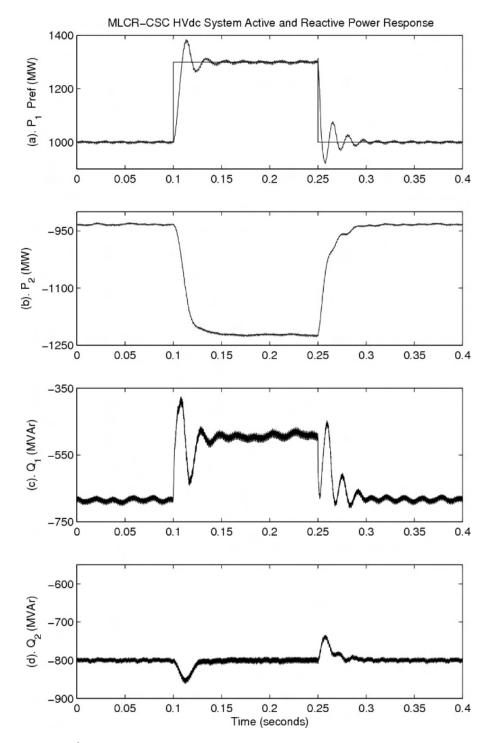

|       | 11.3.3 Simulated Performance under Normal Operating Conditions | 345 |

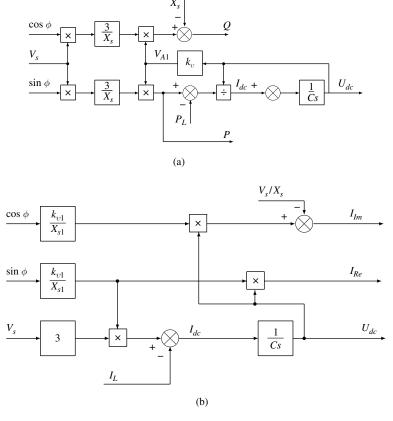

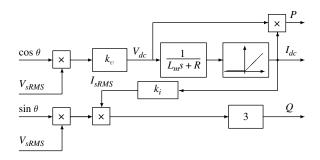

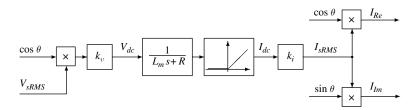

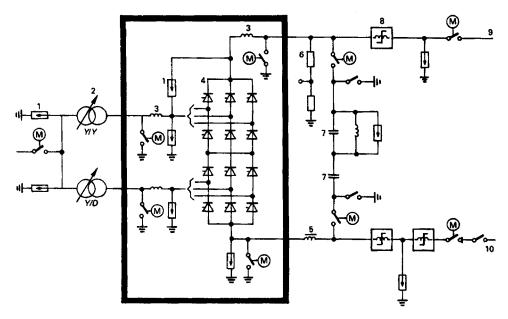

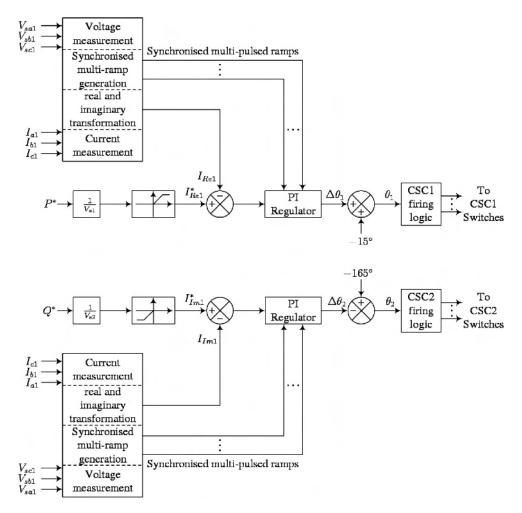

|       | 11.3.2 Control Structure                                       | 344 |

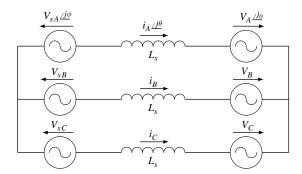

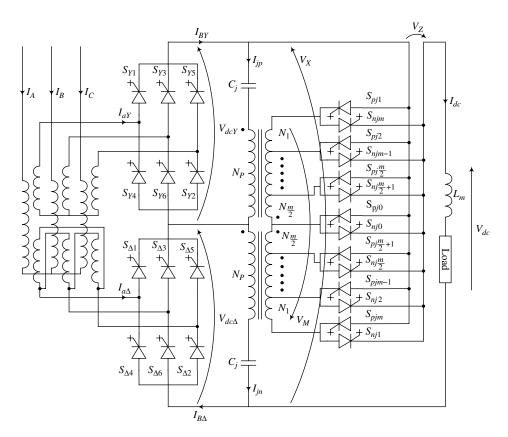

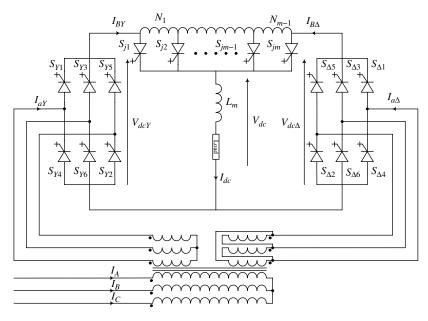

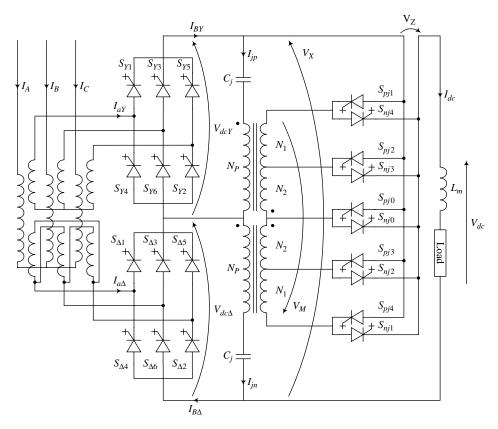

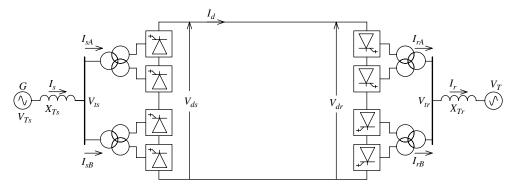

|       | 11.3.1 Dynamic Model                                           | 343 |

| 11.3  | Multi-Level CSC Transmission                                   | 341 |

|       | 11.2.4 Provision of Independent Reactive Power Control         | 337 |

|       | 11.2.3 Test System and Simulation Results                      | 332 |

# **Preface**

The structure and characteristics of HVDC (High-Voltage Direct Current) converters have remained practically unaltered for the first 40 years of commercial operation. Restricted by the switching characteristics, first of the mercury arc valve and later of the silicon-controlled rectifier, this technology requires substantial extra support at the link terminals to ensure stable operation.

More recently the development of power semiconductors with improved characteristics has provided the basis for a flexible AC transmission system (FACTS) technology. This technology covers a variety of power electronics controllers created to enhance the performance of the traditional grid. The individual members of the FACTS family are designed to solve a specific problem, e.g. active or reactive power flow control, short-circuit current limitation, etc. So it is the complete family that provides transmission flexibility, rather than the individual controllers.

The new power semiconductors have also, in the past decade, changed the attitude towards HVDC transmission, and a variety of converter configurations have been developed to take advantage of the higher controllability and switching frequencies of the new devices.

Although the main market for HVDC is still thyristor based, a transistor-based technology has recently been developed, and is already being used throughout the world. The new HVDC technology can provide most of the enhancements of the individual FACTS controllers, i.e. permit large stable power transfers, deliver or absorb the required reactive power to maintain the specified voltages at the interconnected buses, contain fast emergency controls to avoid large fault current levels, be designed (if required) to control sub-synchronous resonances, etc. Moreover, the DC link is the only practical way of connecting asynchronous systems and systems of different frequencies. For a given HVDC configuration, all these tasks can be achieved purely by control action.

Therefore, a modern HVDC interconnection is potentially the most flexible power transmission system. However, the provision of greater HVDC transmission flexibility comes at a price, in terms of either reduced efficiency or increased structural complexity. Thus, when considering a new scheme, it is important to decide on the degree of flexibility required for the particular application (i.e. taking into account power ratings, transmission distances, extent of ancillary services expected, etc.).

A critical review of the HVDC options already available and under consideration constitutes the purpose of this book, which therefore complements recent titles describing the FACTS technology to help power system engineers to make informed decisions on the planning, design and operation of future power transmission systems. It is also a useful reference text for students taking advanced courses in power transmission.

xii PREFACE

The first five chapters describe the principles and components of existing converter technology. Chapters 6 and 7 discuss alternative proposals for self-commutating conversion and Chapters 8, 9, 10 and 11 the application of the various converter configurations to HVDC transmission.

The authors would like to acknowledge the main sources of information that have made the book possible and in particular the material reproduced, with permission, from CIGRE Study Committee B4 and ABB industry documents.

At the personal level they wish to acknowledge the services of Greta Arrillaga (who half a century ago also typed the first book on the subject of HVDC by Adamson and Hingorani!), the advice received from Alan Wood and Nick Murray of Canterbury University, Dennis Woodford of Electranix and Gunnar Asplund of ABB.

They also wish to thank The University of Canterbury and The University of Inner Mongolia for providing the facilities for their work.

1

# Introduction

#### 1.1 The Conventional Power Grid

The power sources in conventional power systems must operate at exactly the same frequency and in perfect synchronism. Each generator controls the magnitude of its terminal voltage by the excitation current and the phase angle of this voltage by means of the mechanical torque developed by the turbine. The generators are designed to produce relatively low voltages, and thus the generated power undergoes a number of voltage transformations, from low to high voltage (for efficient power transmission) and from high to medium and low voltage (for economic and safe power distribution). These changes are implemented by power transformers.

Within a national grid, the use of a fully interconnected primary transmission system, to which the new power stations are connected, has traditionally been the generally accepted philosophy behind the development of an efficient power system.

The expansion of the primary transmission system was normally continued until the rated switchgear fault level was exceeded. Beyond that point a new primary transmission system, of higher voltage and fault levels, was created, while the previous one continued expanding into several separate (secondary) systems. Each of these secondary transmission systems in turn supplied a number of distribution (normally radial) feeders. So the conventional power grid has traditionally been grouped into three separate parts, i.e. generation, transmission and distribution, all of them inflexibly tied by the synchronous constraints.

#### 1.1.1 Power Transfer Mechanism

Transformers, generators and transmission lines are predominantly inductive, and most loads have an inductive component as well. The presence of inductance delays the current response of these components to the voltage variation across them, and this effect causes phase shifts between the voltage and current waveforms which affect the efficiency of the power transmission process.

The instantaneous power (p) associated with a power system component is the product of the instantaneous values of the voltage (v) and current (i) at its terminals (p = vi). The integration of the instantaneous power variation over a complete cycle divided by the period of repetition, i.e.

$$(1/T)\int_{t}^{t+T} pdt$$

provides the average or *active power*. If both the voltage and current vary sinusoidally at the same frequency, in terms of rms (root mean square) voltage (V) and current (I) quantities, the active power is expressed as

$$P = VI\cos(\phi) \tag{1.1}$$

where  $\phi$  is the phase angle between the voltage and the current fundamental frequency waves.

As the rms values are always positive, the product VI (referred to as volt-ampere or apparent power), gives no indication of the active power sign. It is the sign of  $\cos(\phi)$  (the *power factor*) that determines whether the circuit component is generating or absorbing power.

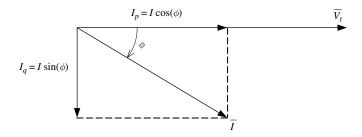

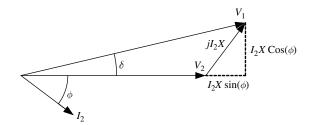

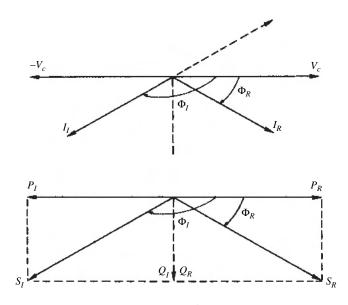

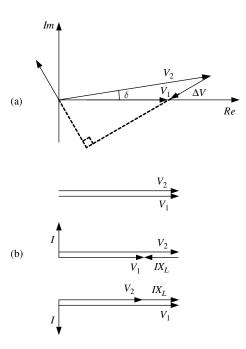

In Figure 1.1, using the voltage as the phase angle reference and resolving the current into in-phase  $(I_p)$  and quadrature  $(I_q)$  components, the product of V and  $I_p$  is clearly the active power, while the product of V and the quadrature component  $I_q$ , i.e.

$$Q = VI\sin(\phi) \tag{1.2}$$

is referred to as reactive power.

Reactive power is needed to establish the magnetic and electrostatic fields; it is temporarily stored and then released (i.e. it consists of positive and negative regions within the cycle). In fact the energy associated with the reactive power oscillates between the element and the rest of the circuit (at the rate of two reversals per period). Although the reactive power has a zero average value, it still represents real reciprocating energy that must be present by virtue of the inductance or capacitance of the network.

When  $\phi$ , the phase angle difference in Equation (1.2), is between 0 and  $\pi$ ,  $\sin(\phi)$  is positive and the circuit element is said to be a consumer of Q; similarly, when  $\phi$  is between  $\pi$  and  $2\pi$ ,  $\sin(\phi)$  is negative and the element is said to be a generator of Q. The convention

Figure 1.1 In-phase and quadrature current components

used is that when Q is positive the current lags the voltage and when Q is negative the current leads the voltage

Squaring the expressions of P and Q in Equations (1.1) and (1.2) and adding them gives

$$(VI\cos(\phi))^{2} + (VI\sin(\phi))^{2} = (VI)^{2}$$

(1.3)

and

$$VI = \sqrt{P^2 + Q^2} \tag{1.4}$$

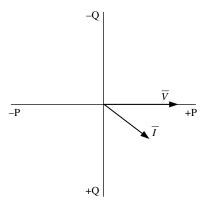

Equations (1.3) and (1.4) can be represented in a four-quadrant complex diagram, as shown in Figure 1.2, with the axes labelled  $\pm P$  and  $\pm jQ$ .

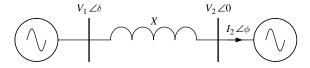

### Power transfer between active sources

Figure 1.3 shows a purely inductive line interconnecting two ideal voltage sources  $V_1$  and  $V_2$  (which can be either generators or nodes of a synchronous system). The phasor diagram in Figure 1.4 represents the operating condition when the voltage at terminal 1 leads that of terminal 2 by an angle  $\delta$  (referred to as the power angle) and the current at terminal 2 lags its voltage by an angle  $\phi$  (referred to as the power factor angle). Using the voltage of terminal 2 as a phase reference, the following expressions are derived from this diagram:

$$I_2 X \cos(\phi) = V_1 \sin(\delta) \tag{1.5}$$

$$I_2 X \sin(\phi) = V_1 \cos(\delta) - V_2 \tag{1.6}$$

Figure 1.2 Four-quadrant diagram with the voltage as reference

Figure 1.3 Interconnection between two synchronous systems

**Figure 1.4** Phasor diagram for the interconnection of Figure 1.3

From Equations (1.5) and (1.6) the active and reactive power transfers become

$$P = V_2 I_2 \cos(\phi) = \frac{V_1 V_2 \sin(\delta)}{X} \tag{1.7}$$

$$Q = V_2 I_2 \sin(\phi) = \frac{V_2 (V_1 \sin(\delta) - V_2)}{X}$$

(1.8)

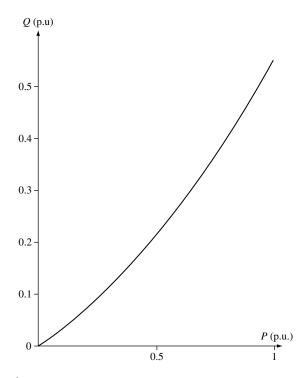

Thus to control the P and/or Q transfers it is necessary to vary one or more of the four variables  $V_1$ ,  $V_2$ ,  $\delta$  and X in Equations (1.7) and (1.8). As indicated earlier, the generated voltage phase and magnitude values can be controlled by the turbine governor and generator excitation respectively. However, from the power transmission viewpoint, the generator controls are slow and inefficient: the slow control imposes a power transmission restriction on the steady-state operating point, as the power angle  $\delta$  in Equation (1.7) has to be kept low in order to preserve transmission stability following large disturbances; also the relatively large requirement of reactive power (Equation (1.8)) will overload unnecessarily the generation and transmission systems.

#### Power transfer to a consumer load

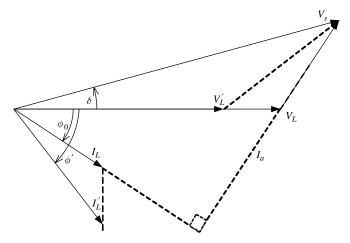

Consumer loads are connected to radial feeders, normally at the end of the power distribution network. Low power factor loads have a detrimental effect on the load voltage and, therefore, on the power transfer capability. This effect is illustrated with reference to Figure 1.5 on the assumption that the feeder and the primary system behind it are represented by a voltage source  $(V_s)$  in series with a total system reactance  $(X_s)$ . To maintain the active power constant when the power factor reduces (i.e. angle  $\phi$  increases) requires an increase in the load current, i.e.  $I'_L > I_L$ ; this increase causes a higher voltage drop in the system reactance which, in turn, reduces the load voltage  $(V_L)$ .

Thus to maintain the required power level, either the source voltage must increase or some means of voltage support must be provided locally. For instance, the latter can be achieved by connecting a capacitance in parallel with the load. This will add a quadrature component to the load current and will reduce the overall current in the feeder; this solution is referred to as *power factor correction*. However, the use of local compensation by means of passive components, although efficient, is neither fast nor continuous and increases the likelihood of low-order harmonic resonance with the system impedance.

Figure 1.5 Effect of the load power factor on the load voltage

### 1.2 Towards a More Flexible Power Grid

A variety of technical, economical and environmental reasons affecting the generation, transmission and utilisation of power are forcing a rethink on the conventional power system development philosophy. The dilemma is that, on the one hand, there is growing opposition to the acceptance of new transmission lines and ever increasing primary transmission voltages. On the other hand, there is the realisation that power system interconnections bring undisputable benefits, such as economies of scale, wider choices of generating plant, reductions in reserve capacity, diversity in demand, supply reliability, pooling opportunities, etc.

Clearly an important factor in the solution is the possibility of increasing the power carrying capability of the transmission lines. In this respect conventional AC transmission is severely restricted by the need to keep the two systems interconnected by the line in synchronism following disturbances (i.e. when the phase difference between the terminal voltages increases rapidly), a condition referred to as transient stability. Therefore increases in the steady-state power carrying capability are linked to improvements in the transient stability levels, which in turn require faster controllability. Controllability and flexibility are used in power transmission as synonymous terms; in other words, greater flexibility implies greater and faster controllability. The latter has been made possible by the development of power semiconductors (discussed in Chapter 2) and their application to the control of power apparatus and systems, commonly referred to as power electronics.

#### 1.2.1 Power Electronics Control

The advent of power electronics technology has been the catalyst for the provision of greater grid flexibility. A power electronics controller can be broadly described as a matrix of static switches connecting a number of input nodes to a number (not necessarily the same) of output nodes and the power flow may be in either direction. The circuits behind these nodes may be either DC or AC and predominantly inductive or capacitive.

The application of power electronics in power transmission systems has led to the development of two complementary technologies, referred to as HVDC (High-Voltage Direct Current) [1–5] and FACTS (Flexible AC Transmission System) [6–7]. However, only the latter has so far used the term flexibile, which is often interpreted as an exclusive characteristic of this technology. This book widens the flexibility concept by discussing HVDC technology under the umbrella of flexible power transmission.

Both HVDC and FACTS make extensive use of AC–DC static power conversion; the basic characteristics of this process are discussed in the next section.

### Static power conversion

Within the power electronics discipline, the designation AC–DC static power conversion is used for the processes of rectification and inversion, which provide the basis for fast power controllability. As well as improving controllability, these two processes, when applied to DC transmission, also remove the synchronous constraints. The first consideration in the process of static power conversion is how to achieve instantaneous matching of the AC and DC voltage levels, given the limited number of phases and switching devices that are economically viable. The following circuit restrictions are imposed on a static power converter by the characteristics of the external circuit and of the switching components:

- If one set of nodes (input or output) of the matrix of switches is inductive, the other set

must be capacitive so as not to create a loop consisting of voltage sources (or capacitors

and voltage sources) when the switches are closed or a cut set consisting of current

sources when the switches are opened.

- 2. The combination of open and closed switches should not open-circuit an inductor (except at zero current) or short-circuit a capacitor (except at zero voltage).

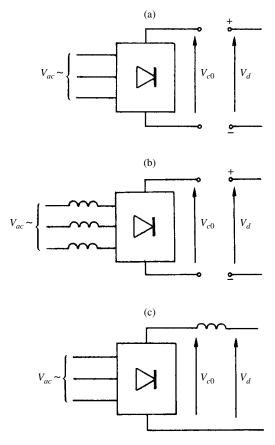

For stable conversion some impedance must, therefore, be added to the switching circuit of Figure 1.6(a) to absorb the continuous voltage mismatch that inevitably exists between the two sides. If the impedance is exclusively located on the AC side (as shown in Figure 1.6(b)), the switching devices transfer the instantaneous direct voltage level to the AC side and, thus, the circuit configuration is basically a voltage source converter (referred to as VSC), with the possibility of altering the DC current by controlling the turn-on and turn-off instants of the switching devices.

If, instead, a large smoothing reactor is placed on the DC side (as shown in Figure 1.6(c)), pulses of constant DC flow through the switching devices into the AC side. Then, a basically current source converter results (referred to as CSC), again with the possibility of adjusting the direct voltage by appropriate switching control. CSC is the more practical alternative when using thyristor switches without turn-off controllability.

Another classification relates to the source of the commutation process between the converter valves. When the source is the AC system voltage the converter is said to be line-commutated (LCC). LCC relies on the natural current zeros created by the external circuit for the transfer of current from switch to switch. CSC-LCC is the only

**Figure 1.6** AC–DC voltage matching: (a) unmatched circuit; (b) circuit for voltage conversion; (c) circuit for current conversion

practical alternative when using thyristor switches without turn-off capability. This is still the most common solution for DC transmission, even though it is the least flexible, and is discussed in Chapter 3.

The alternative is self-commutation (a process described in Chapter 4), which is achieved independently from the external circuit components by the use of advanced switching devices with turn-off capability and, thus, provides greater flexibility.

Static power converters are also classified by the principle, and related configurations, used to produce the output waveforms. The most flexible alternative, in this respect, is the use of a simple (normally two-level) converter configuration and a complex sub-cycle waveform control. This subject, discussed in Chapter 5, uses a high-frequency carrier signal to modulate the required waveform and is, thus, referred to as pulse width modulation (PWM).

The second principle in the self-commutating category is the derivation of a stepped (multi-pulse or multi-level) waveform using only fundamental frequency switching. This concept, discussed in Chapters 6 and 7, is more efficient but less flexible than PWM, and it involves a greater number of components.

The main technical requirements of static converters for high-power applications are:

- 1. The provision of high-voltage valves with balanced voltages across the series-connected individual switches during the off-state and in the dynamic regions.

- 2. The ability to achieve high-quality output waveforms.

- 3. Limitation of the dv/dt rate across the switches and other converter components to simplify insulation coordination and reduce RF interference.

- 4. The ability to achieve high efficiency by reducing on-state and switching losses.

- 5. Simplification of the topology to reduce component costs.

- 6. Flexibility in terms of active and reactive power controllability.

### 1.3 HVDC Transmission

The original motivation for the development of DC technology was transmission efficiency, as the power loss of a DC line is lower than that of a corresponding AC line of the same power rating. However, this required the use of HVDC and, therefore, the development of conversion switches capable of withstanding high voltages

The invention of the high-voltage mercury valve half a century ago paved the way for the development of HVDC transmission. By 1954, the first commercial DC link came successfully into operation and was soon followed by several other schemes orders of magnitude larger. The success of the new technology immediately triggered research and development into an alternative solid-state valve, which by the mid-1960s had already displaced the use of mercury arc valves in new schemes. The early history and technical development of the HVDC technology are described in [8].

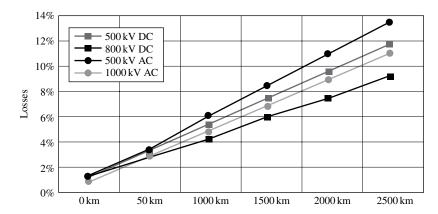

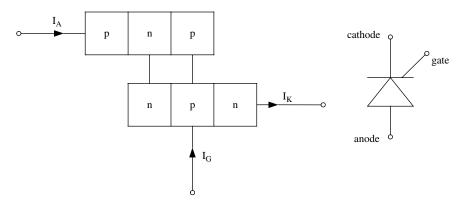

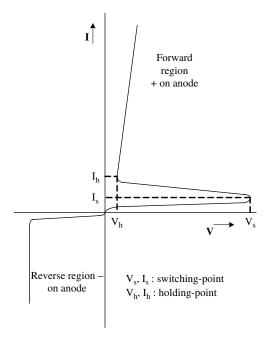

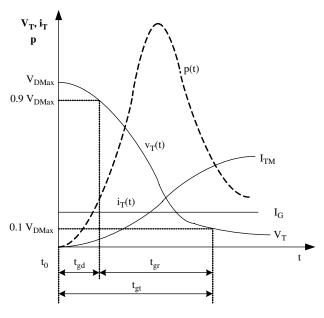

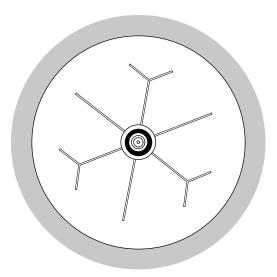

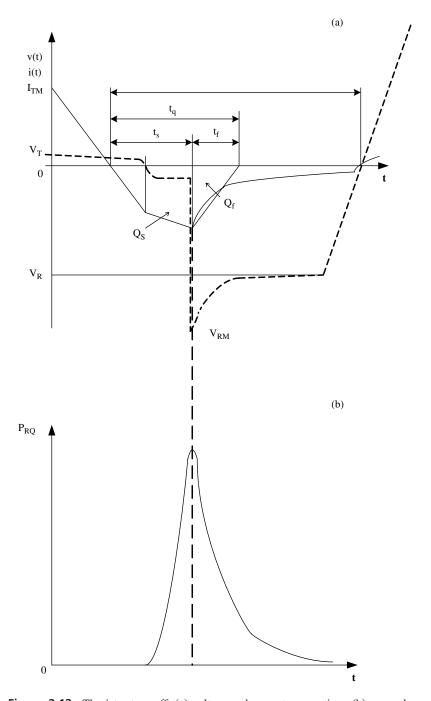

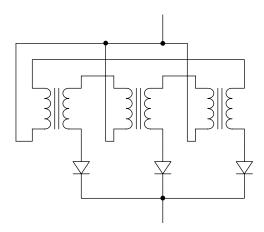

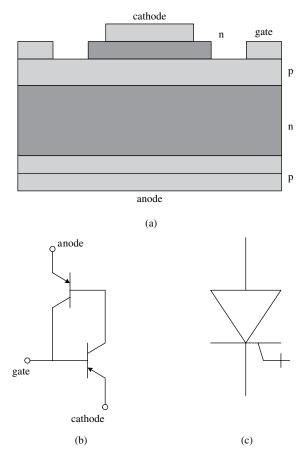

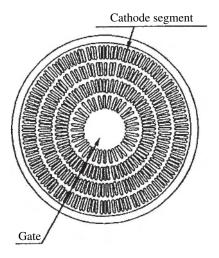

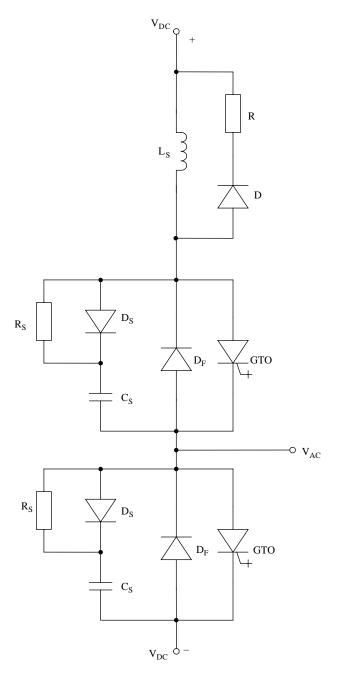

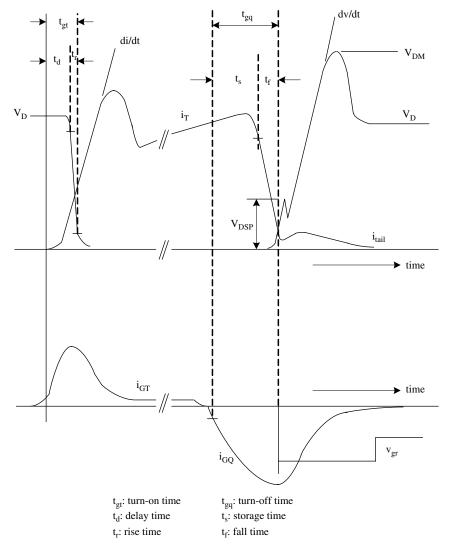

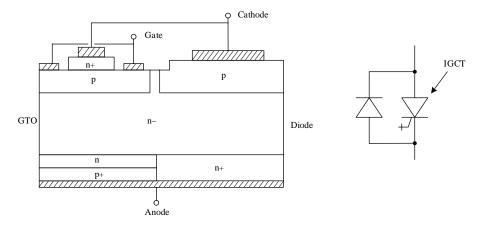

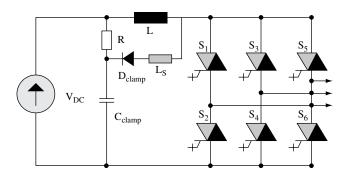

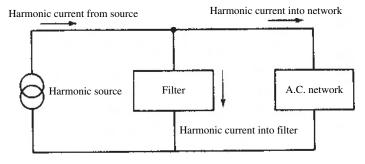

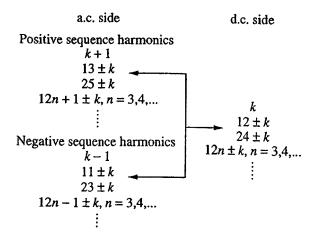

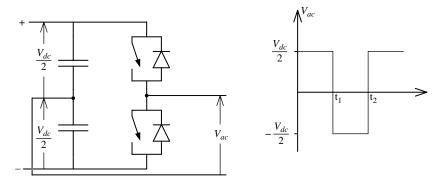

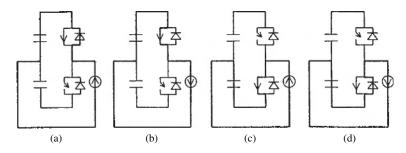

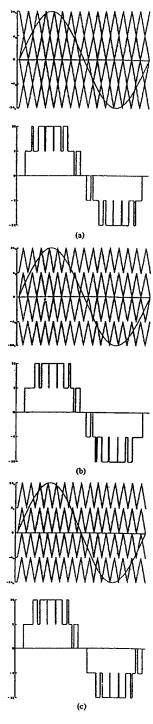

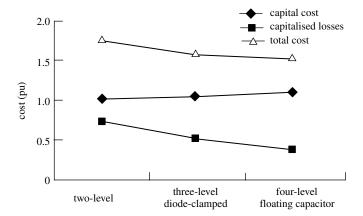

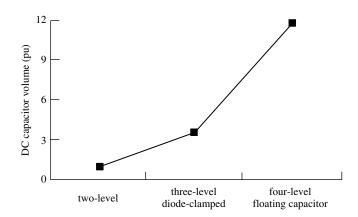

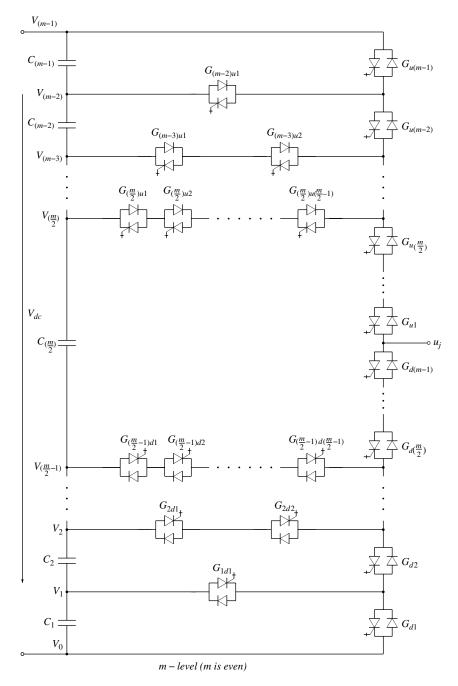

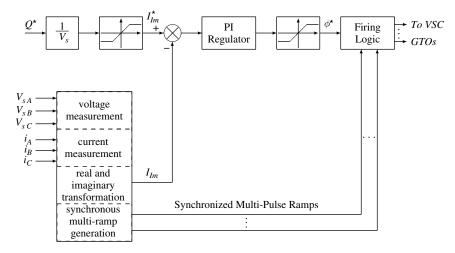

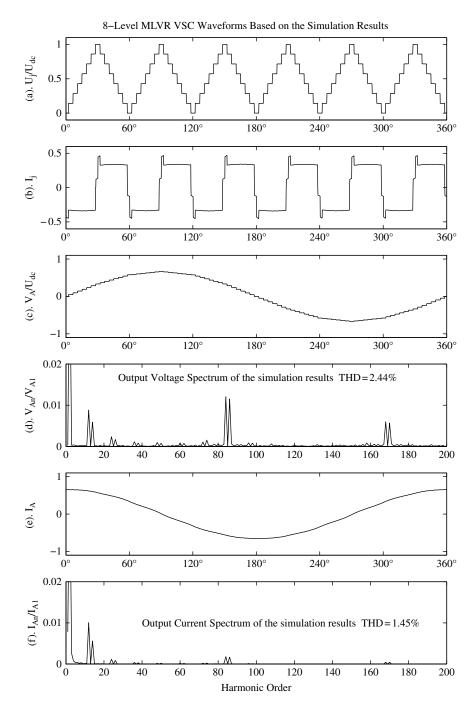

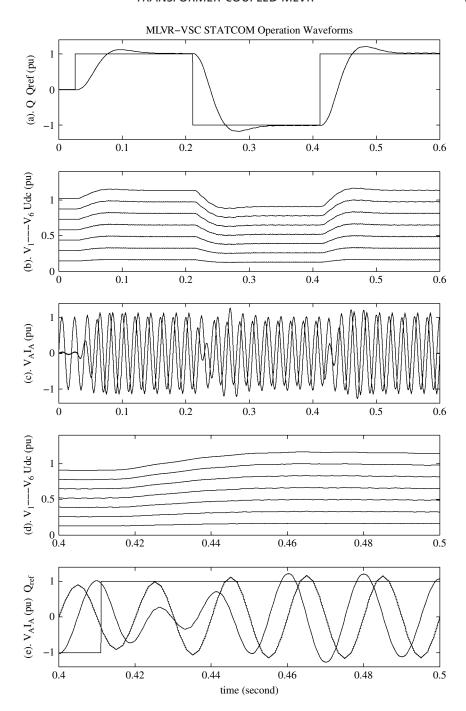

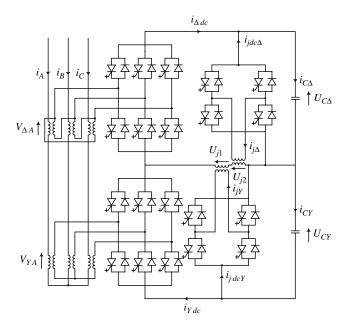

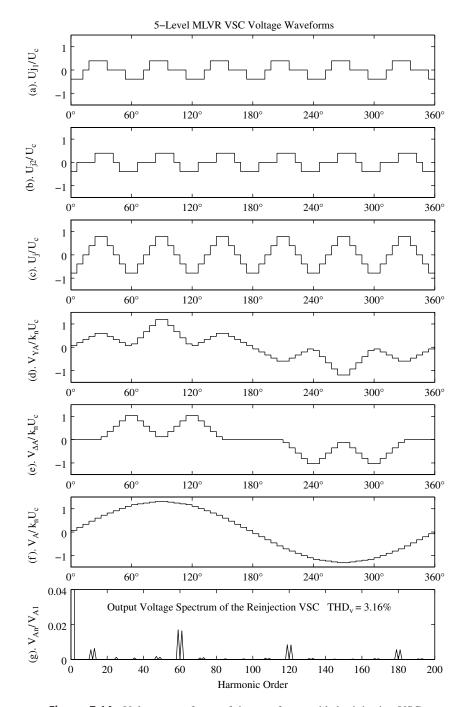

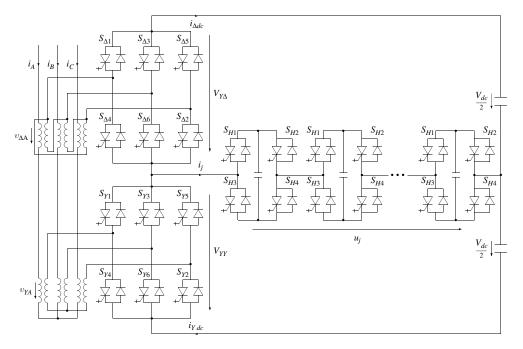

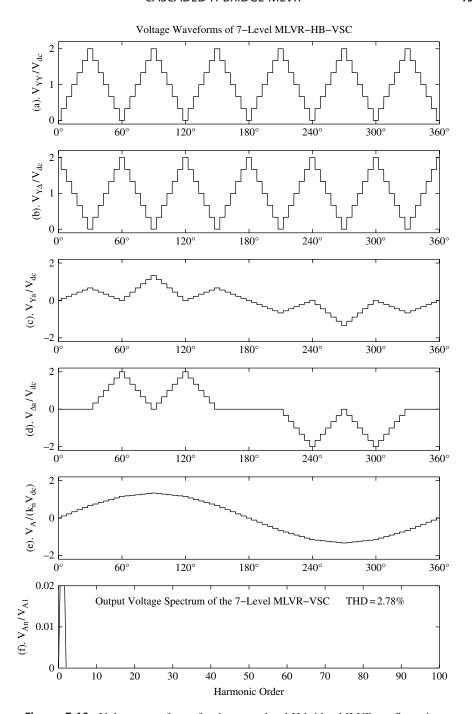

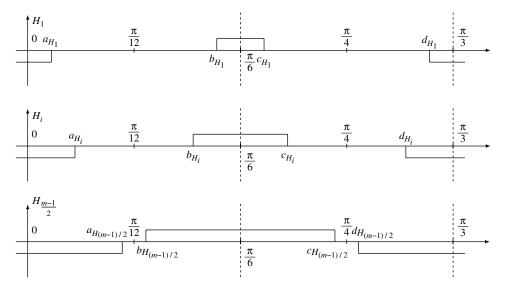

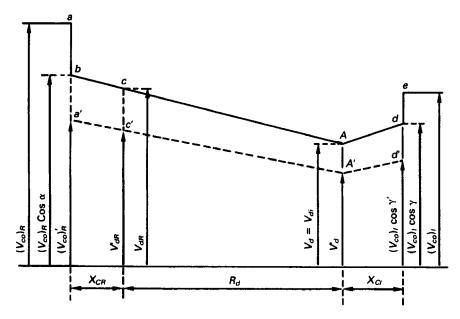

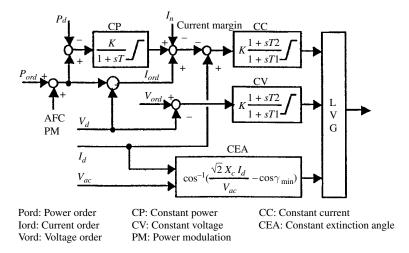

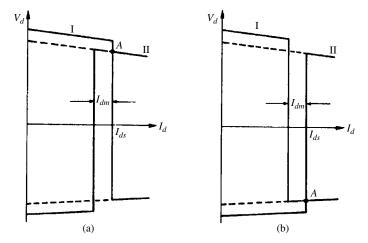

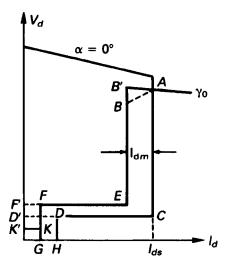

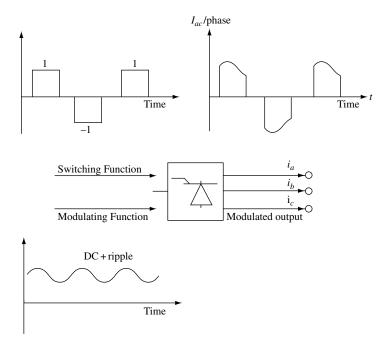

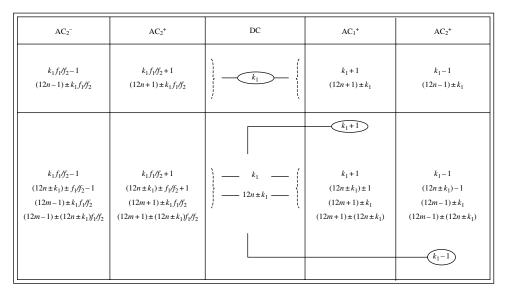

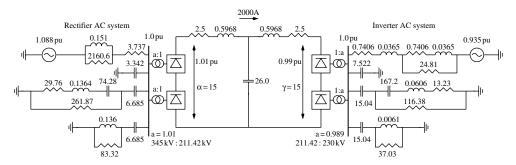

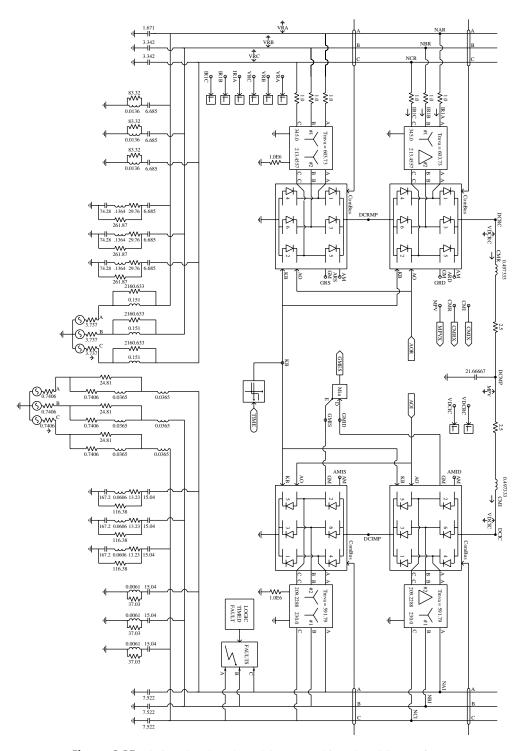

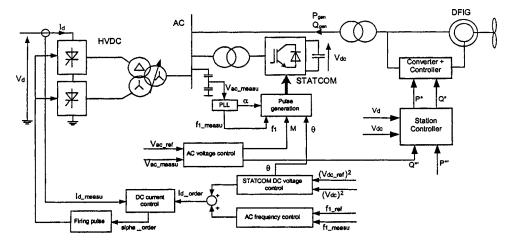

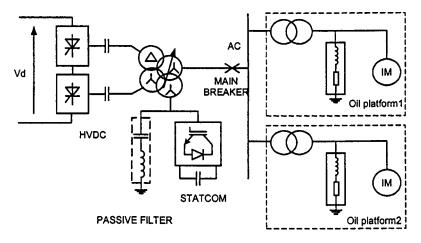

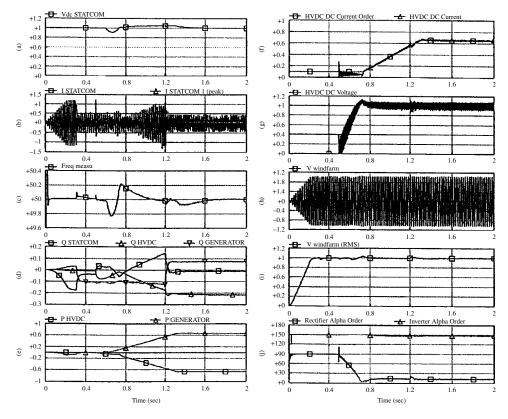

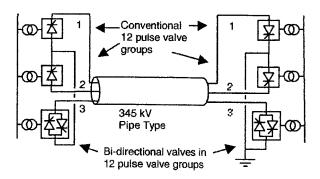

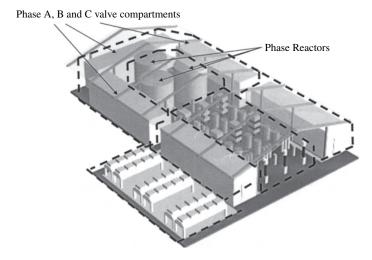

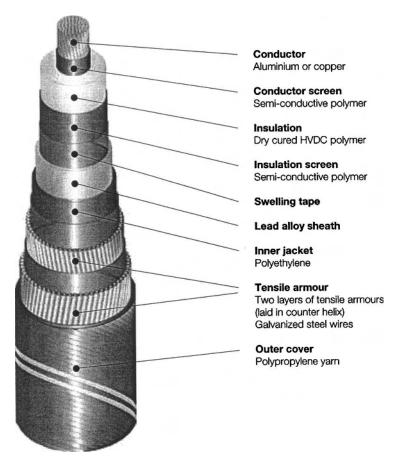

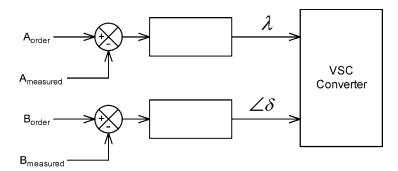

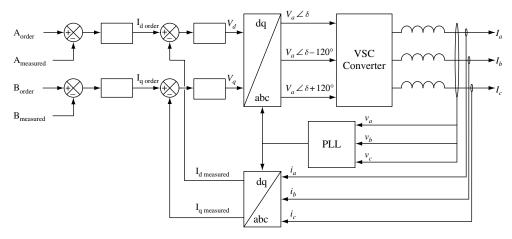

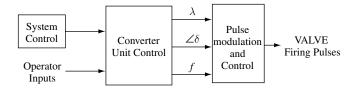

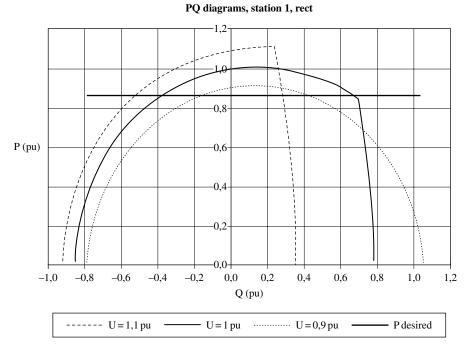

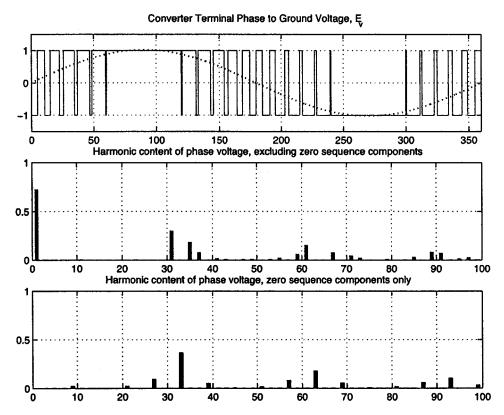

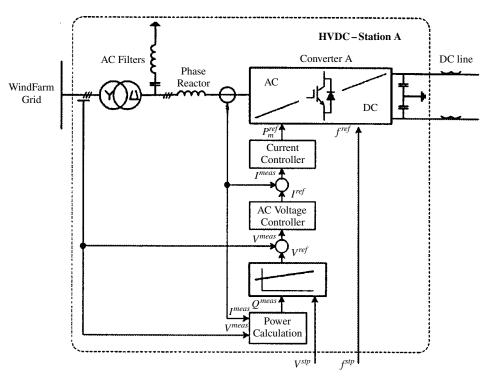

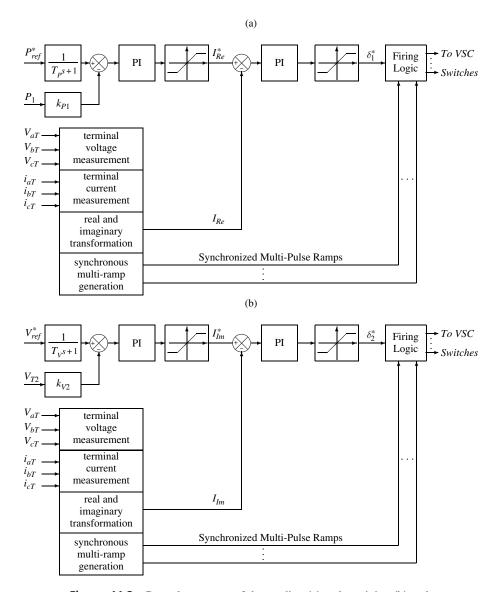

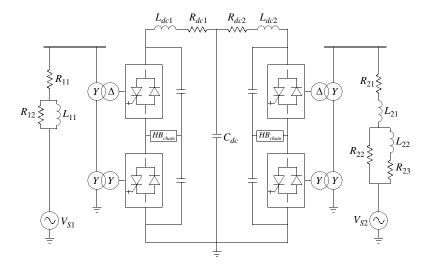

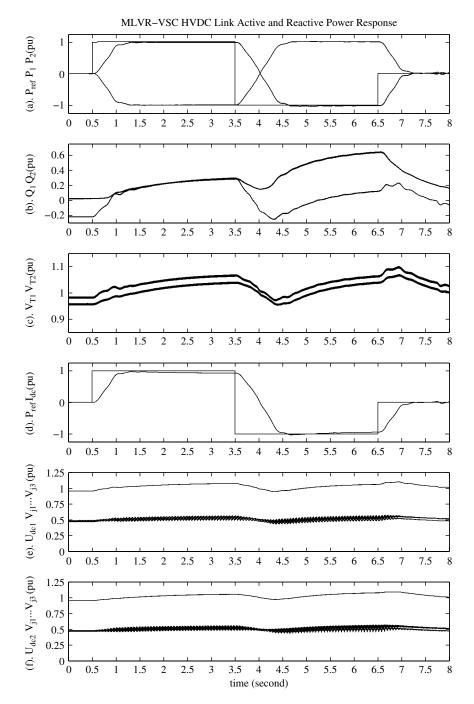

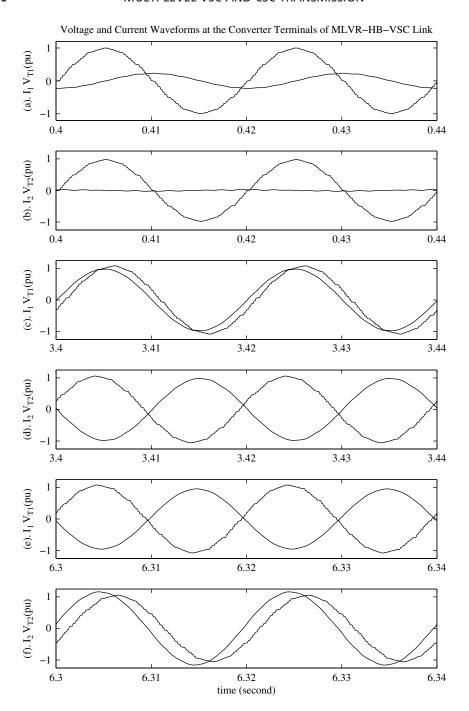

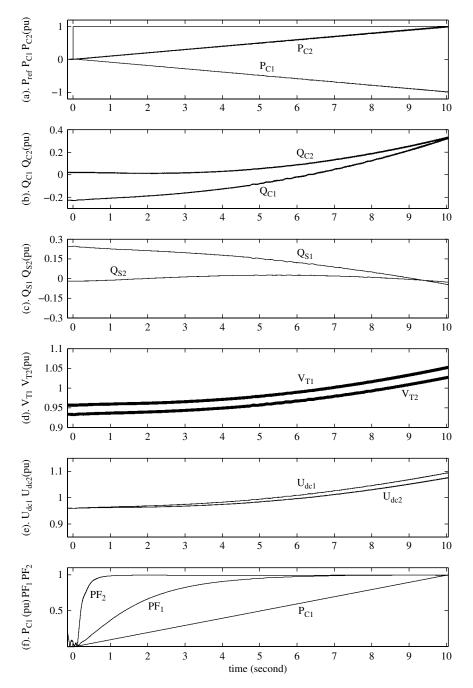

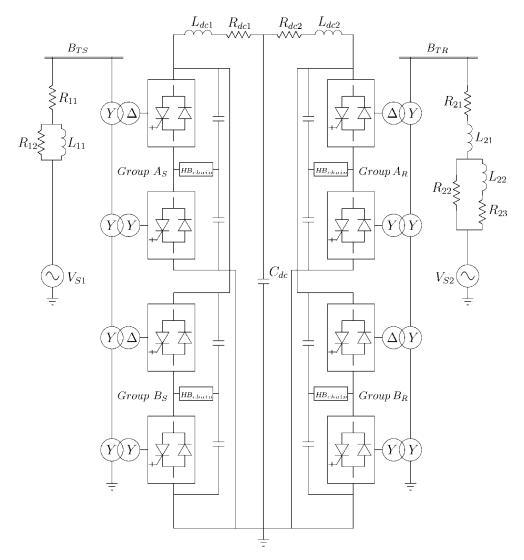

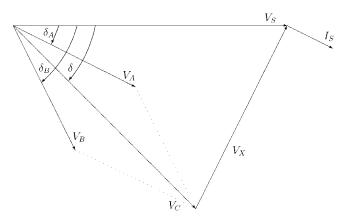

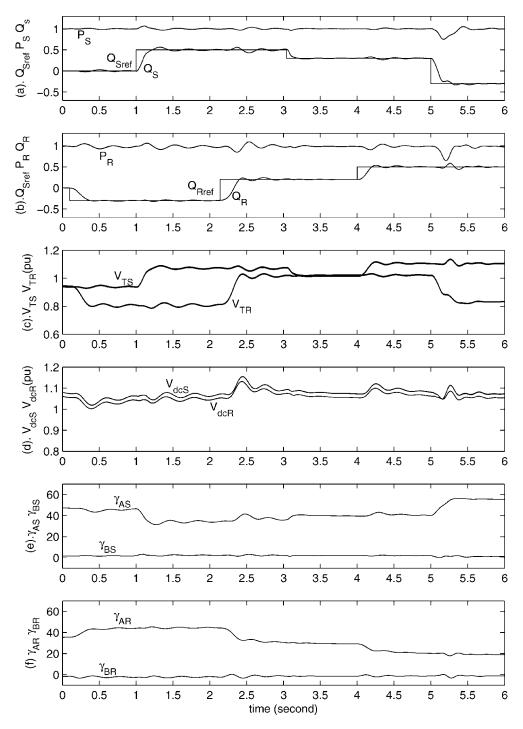

Substantial progress made in the ratings and reliability of thyristor valves has increased the competitiveness of HVDC schemes. DC transmission has lower transmission losses and cost than equivalent AC lines, but requires terminal equipment which adds to the cost and power losses. Thus traditionally, the DC option has been found economically viable only when the distance involved is long and the amount of energy to be transferred large. However, there are other factors that must be taken into consideration in the selection of an HVDC interconnection. An important factor in the economic comparison between AC and DC interconnections is to determine whether synchronisation of the previously separate systems is feasible and economical.