# Computer Systems Architecture

A Networking Approach Rob Williams

Second Edition

### Computer Systems Architecture A Networking Approach

Visit the Computer Systems Architecture, second edition Companion Website at www.pearsoned.co.uk/williams to find valuable student learning material including:

- Slides and handouts for each chapter

- Laboratory worksheets

- Example scripts for class phase tests

#### PEARSON Education

We work with leading authors to develop the strongest educational materials in computing, bringing cutting-edge thinking and best learning practice to a global market.

Under a range of well-known imprints, including Prentice Hall, we craft high quality print and electronic publications which help readers to understand and apply their content, whether studying or at work.

To find out more about the complete range of our publishing please visit us on the World Wide Web at: www.pearsoned.co.uk

# Computer Systems Architecture A Networking Approach Second Edition

Rob Williams

Harlow, England • London • New York • Boston • San Francisco • Toronto • Sydney • Singapore • Hong Kong Tokyo • Seoul • Taipei • New Delhi • Cape Town • Madrid • Mexico City • Amsterdam • Munich • Paris • Milan Pearson Education Limited

Edinburgh Gate Harlow Essex CM20 2JE England

and Associated Companies around the world

Visit us on the World Wide Web at: www.pearsoned.co.uk

First published 2001 Second edition 2006

© Pearson Education Limited 2001, 2006

The right of Rob Williams to be identified as author of this work has been asserted by him in accordance with the Copyright, Designs and Patents Act 1988.

All rights reserved; no part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise without either the prior written permission of the Publishers or a licence permitting restricted copying in the United Kingdom issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP.

All trademarks used herein are the property of their respective owners. The use of any trademark in this text does not vest in the author or publisher any trademark ownership rights in such trademarks, nor does the use of such trademarks imply any affiliation with or endorsement of this book by such owners.

ISBN: 978-0-321-34079-5

British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library.

Library of Congress Cataloging-in-Publication Data Williams, Rob, 1948– Computer systems architecture : a networking approach / Rob Williams. — 2nd ed. p. cm. Includes bibliographical references and index. ISBN-13: 978-0-321-34079-5 ISBN-10: 0-321-34079-5 I. Computer architecture. 2. Computer network architectures. I. Title. QA76.9.A73W545 2006 004.2'2-dc22 2006049522

10 9 8 7 6 5 4 3 2 10 09 08 07

Typeset by 71 Printed and bound by Ashford Colour Press Ltd, Gosport

# Contents

| Preface to the first edition       xx         Recommended lab sessions       xx         Part 1       Basic functions and facilities of a computer         1       Introduction: the hardware–software interface       3         1.1       Computer systems – the importance of networking       4         1.2       Hardware and software – mutual dependence       5         1.3       Programming your way into hardware – VHDL, a language for electronic engineers       6         1.4       Systems administration – we all need to know       5         1.5       Voice, image and data – technological convergence       5 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part 1       Basic functions and facilities of a computer         1       Introduction: the hardware–software interface       3         1.1       Computer systems – the importance of networking       4         1.2       Hardware and software – mutual dependence       5         1.3       Programming your way into hardware – VHDL, a language for electronic engineers       6         1.4       Systems administration – we all need to know       5                                                                                                                                                                     |

| 1       Introduction: the hardware–software interface       3         1.1       Computer systems – the importance of networking       4         1.2       Hardware and software – mutual dependence       5         1.3       Programming your way into hardware – VHDL, a language for electronic engineers       6         1.4       Systems administration – we all need to know       6                                                                                                                                                                                                                                       |

| <ul> <li>1.1 Computer systems – the importance of networking</li> <li>1.2 Hardware and software – mutual dependence</li> <li>1.3 Programming your way into hardware – VHDL, a language for electronic engineers</li> <li>1.4 Systems administration – we all need to know</li> </ul>                                                                                                                                                                                                                                                                                                                                              |

| 1.2Hardware and software – mutual dependence51.3Programming your way into hardware – VHDL, a language for<br>electronic engineers61.4Systems administration – we all need to know6                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| electronic engineers<br>1.4 Systems administration – we all need to know                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.6 Windowing interfaces – WIMPs 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

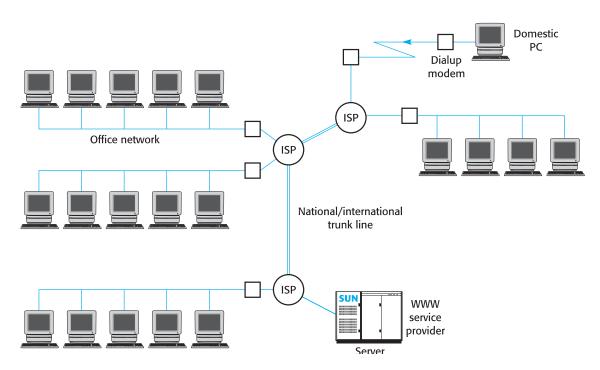

| 1.7 The global Internet – connecting all the networks 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.8 Using the PC – a case study; more reasons to study CSA 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2 The von Neumann Inheritance 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1 Base 2 – the convenience of binary – 10110011100011110000 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2 Stored program control – general-purpose machines 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3Instruction codes – machine action repertoire26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.4 Translation – compilers and assemblers 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.5 Linking – bringing it all together 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

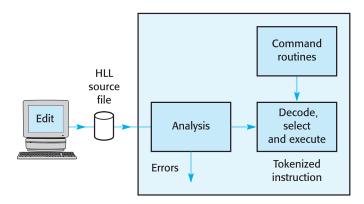

| 2.6 Interpreters – executing high-level commands 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

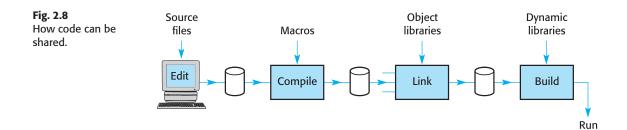

| 2.7Code sharing and reuse – let's not write it all again!312.8Data codes – numeric and character32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.8Data codes – numeric and character322.9The operating system – Unix and Windows36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.9 The operating system – Only and Windows 36<br>2.10 Client–server computing – the way of the Net 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.10 Cleric server computing – the way of the Net 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                                                                   | Functional units and the fetch-execute cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47                                                          |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

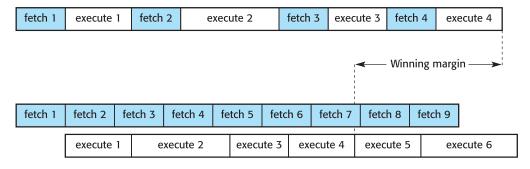

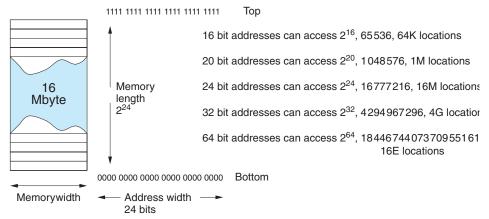

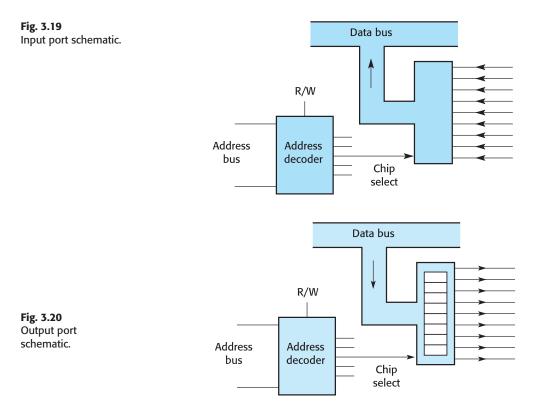

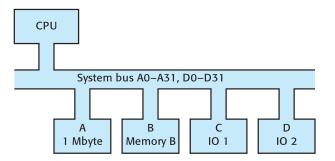

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                | The naming of parts – CPU, memory, IO units<br>The CPU fetch–execute cycle – high-speed tedium<br>System bus – synchronous or asynchronous?<br>System clock – instruction cycle timing<br>Pre-fetching – early efforts to speed things up<br>Memory length – address width<br>Endian-ness – Microsoft vs. Unix, or Intel vs. Motorola?<br>Simple input–output – parallel ports                                                                                                                                                                                              | 48<br>52<br>56<br>59<br>61<br>63<br>65<br>67                |

| 4                                                                   | Building computers from logic: the control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                                                          |

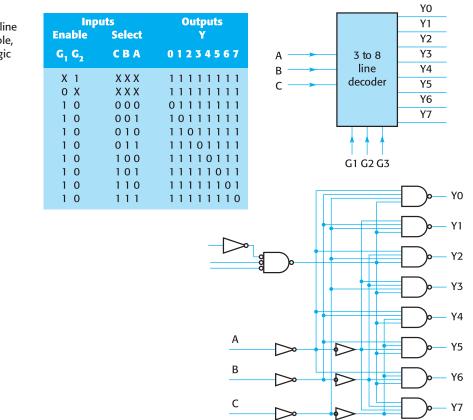

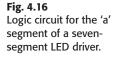

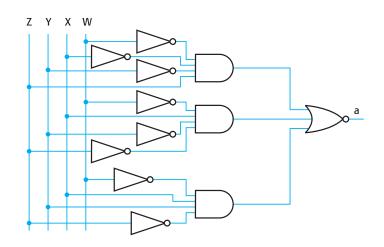

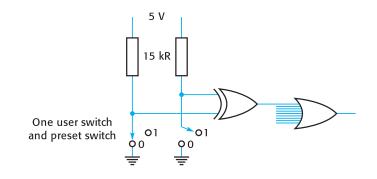

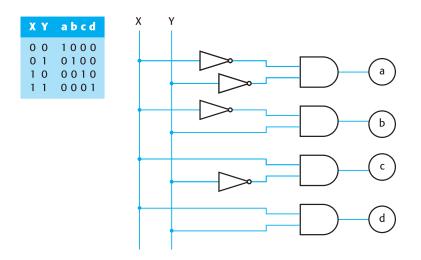

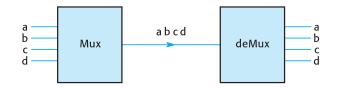

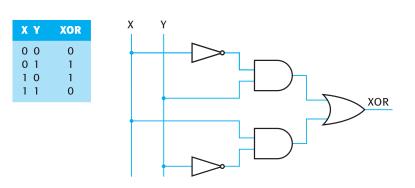

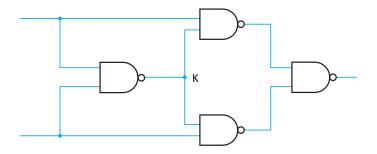

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10 | Electronic Lego and logic – the advantage of modular units<br>Basic logic gates – truth tables for AND, OR, XOR and NOT<br>Truth tables and multiplexers – a simple but effective design tool<br>Programmable logic – reconfigurable logic chips<br>Traffic light controllers – impossible to avoid!<br>Circuit implementation from truth tables – some practical tips<br>Decoder logic – essential for control units and memories<br>CPU control unit – the 'brain'<br>Washing machine controllers – a simple CU<br>RISC vs. CISC decoding – in search of faster computers | 74<br>75<br>77<br>82<br>83<br>85<br>85<br>87<br>88<br>91    |

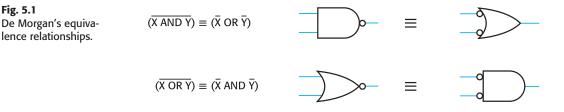

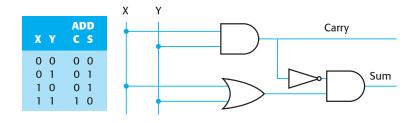

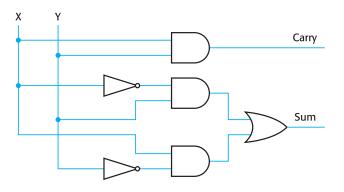

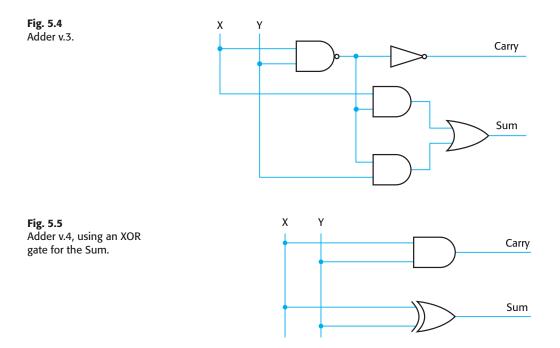

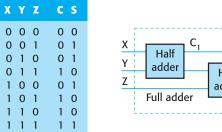

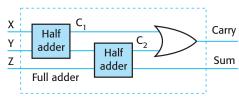

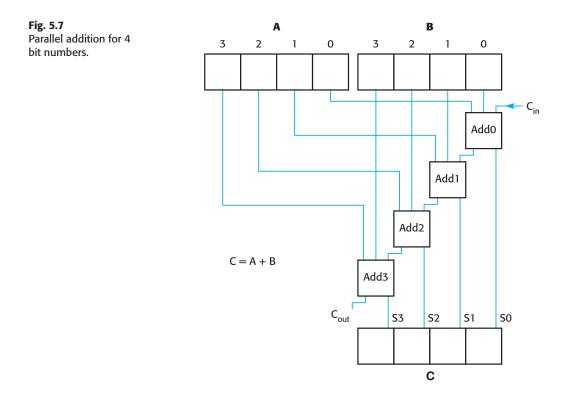

| 5                                                                   | Building computers from logic: the ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 97                                                          |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                              | De Morgan's equivalences – logical interchangeability<br>Binary addition – half adders, full adders, parallel adders<br>Binary subtraction – using two's complement integer format<br>Binary shifting – barrel shifter<br>Integer multiplication – shifting and adding<br>Floating-point numbers – from very, very large to very, very small                                                                                                                                                                                                                                | 98<br>98<br>101<br>103<br>105<br>108                        |

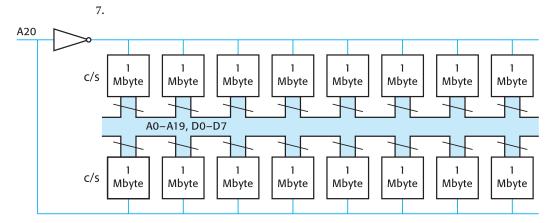

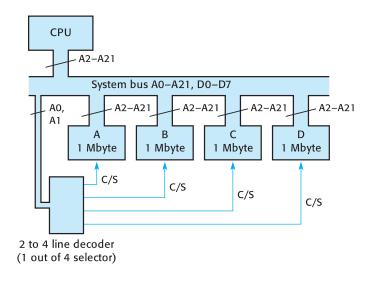

| 6                                                                   | Building computers from logic: the memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 117                                                         |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                | Data storage – one bit at a time<br>Memory devices – memory modules for computers<br>Static memory – a lot of fast flip-flops<br>Dynamic memory – a touch of analogue amid the digital<br>DRAM refreshing – something else to do<br>Page access memories – EDO and SDRAM<br>Memory mapping – addressing and decoding<br>IO port mapping – integration vs. differentiation                                                                                                                                                                                                   | 118<br>120<br>121<br>122<br>124<br>124<br>124<br>127<br>131 |

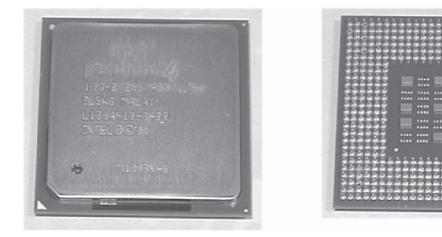

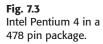

| 7    | The Intel Pentium CPU                                                 | 137 |

|------|-----------------------------------------------------------------------|-----|

| 7.1  | The Pentium – a high-performance microprocessor                       | 138 |

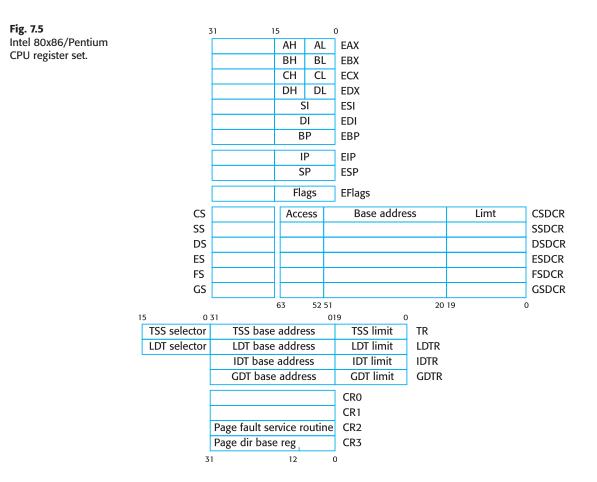

| 7.2  | CPU registers – temporary store for data and address variables        | 143 |

| 7.3  | Instruction set – introduction to the basic Pentium set               | 148 |

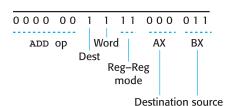

| 7.4  | Structure of instructions – how the CU sees it                        | 149 |

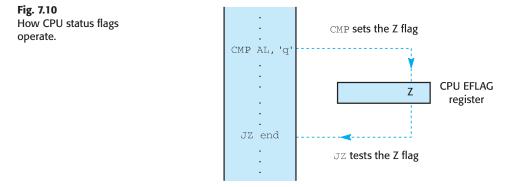

| 7.5  | CPU status flags – very short-term memory                             | 151 |

| 7.6  | Addressing modes – building effective addresses                       | 153 |

| 7.7  | Execution pipelines – the RISC speedup technique                      | 155 |

| 7.8  | Pentium 4 – extensions                                                | 157 |

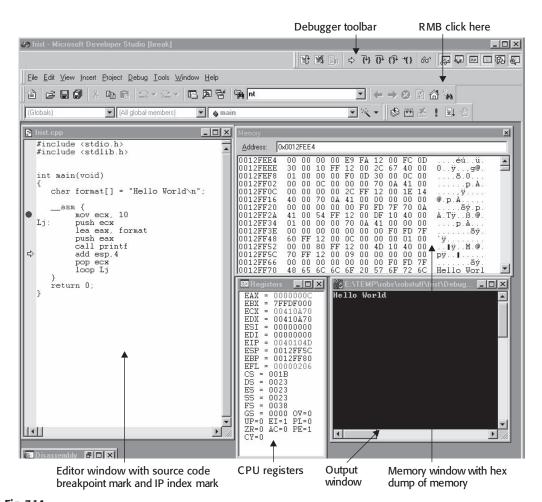

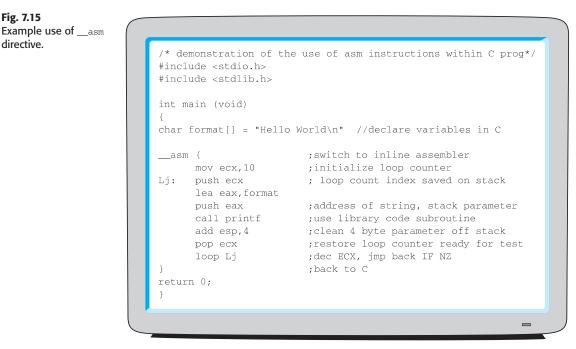

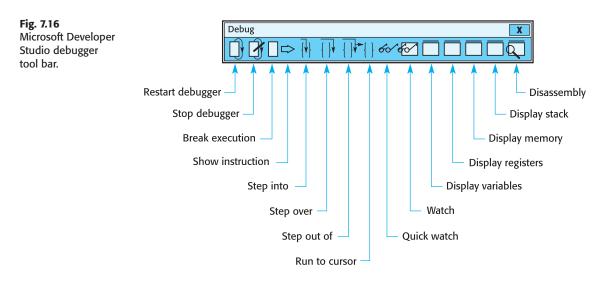

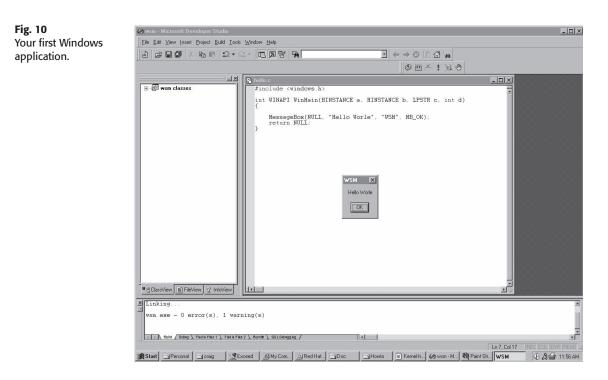

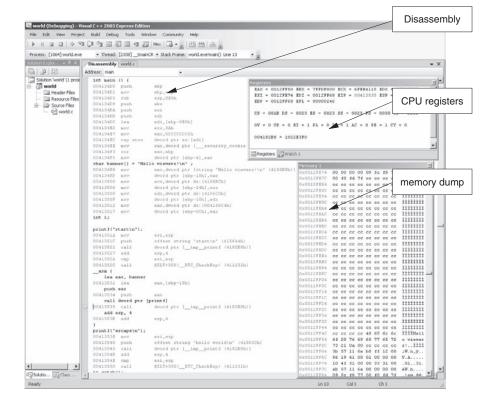

| 7.9  | Microsoft Developer Studio – using the debugger                       | 158 |

| 8    | Subroutines                                                           | 167 |

| 0    | Subroutines                                                           | 107 |

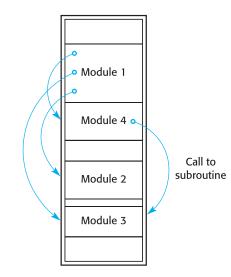

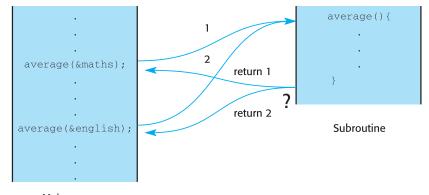

| 8.1  | The purpose of subroutines – saving space and effort                  | 168 |

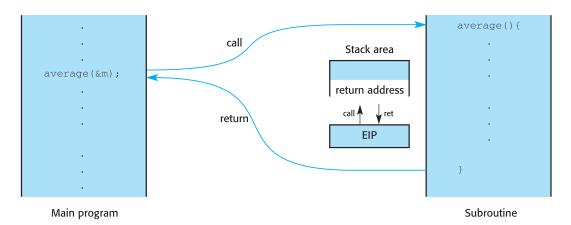

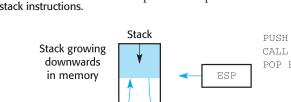

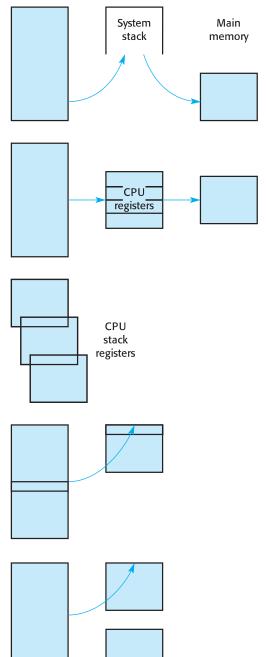

| 8.2  | Return address – introducing the stack                                | 169 |

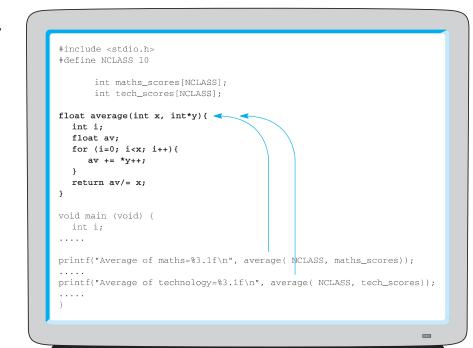

| 8.3  | Using subroutines – HLL programming                                   | 170 |

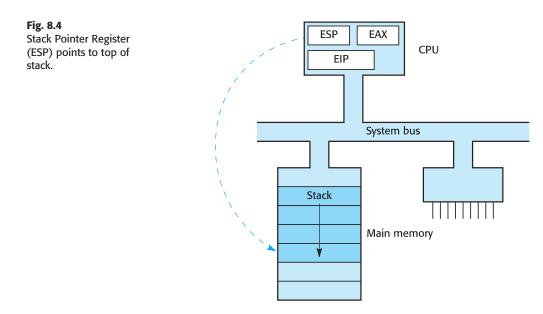

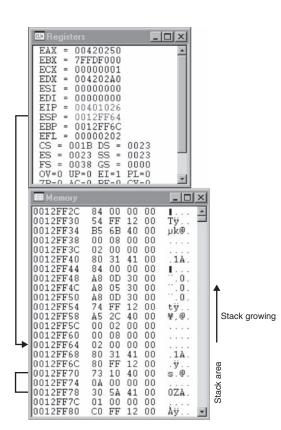

| 8.4  | The stack – essential to most operations                              | 172 |

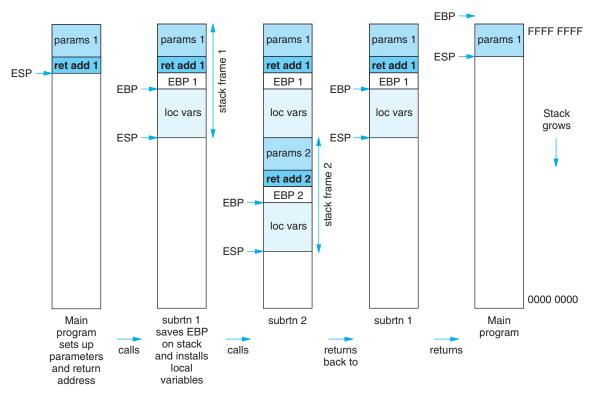

| 8.5  | Passing parameters – localizing a subroutine                          | 173 |

| 8.6  | Stack frame – all the local variables                                 | 176 |

| 8.7  | Supporting HLLs – special CPU facilities for dealing with subroutines | 179 |

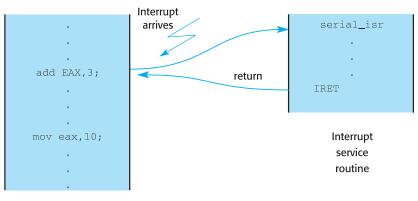

| 8.8  | Interrupt service routines – hardware-invoked subroutines             | 179 |

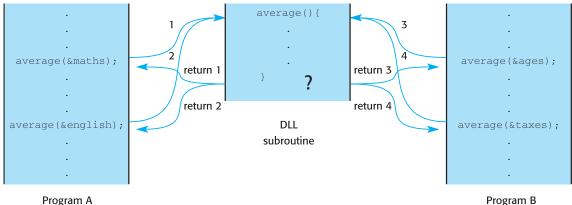

| 8.9  | Accessing operating system routines – late binding                    | 180 |

| 9    | Simple input and output                                               | 185 |

|      |                                                                       | 105 |

| 9.1  | Basic IO methods – polling, interrupt and DMA                         | 186 |

| 9.2  | Peripheral interface registers – the programmer's viewpoint           | 187 |

| 9.3  | Polling – single-character IO                                         | 191 |

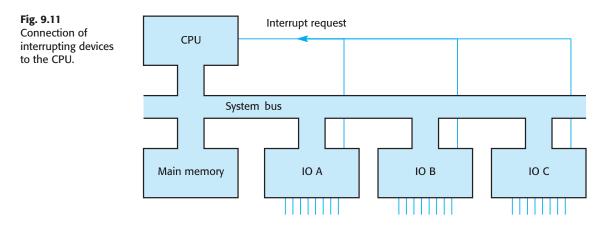

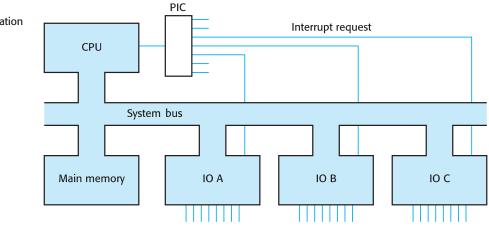

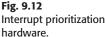

| 9.4  | Interrupt processing – service on demand                              | 197 |

| 9.5  | Critical data protection – how to communicate with interrupts         | 205 |

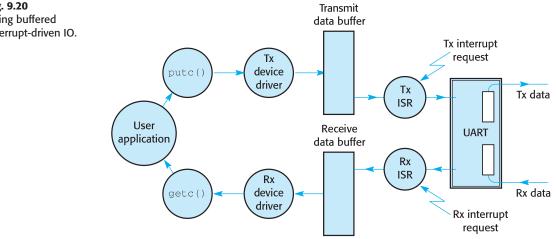

| 9.6  | Buffered IO – interrupt device drivers                                | 209 |

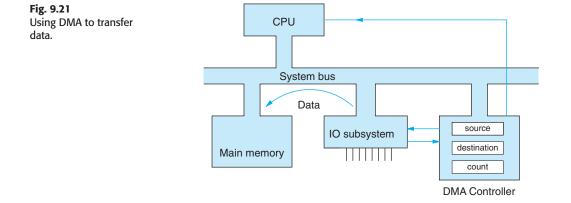

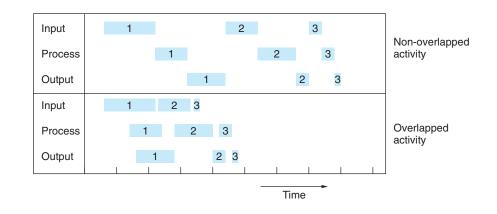

| 9.7  | Direct memory access (DMA) – autonomous hardware                      | 210 |

| 9.8  | Single-character IO – screen and keyboard routines                    | 212 |

| 10   | Serial Connections                                                    | 219 |

| 10   |                                                                       | 215 |

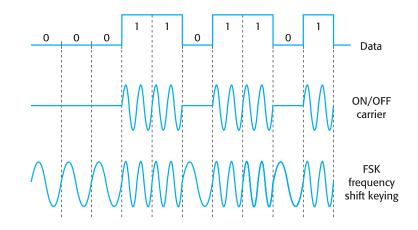

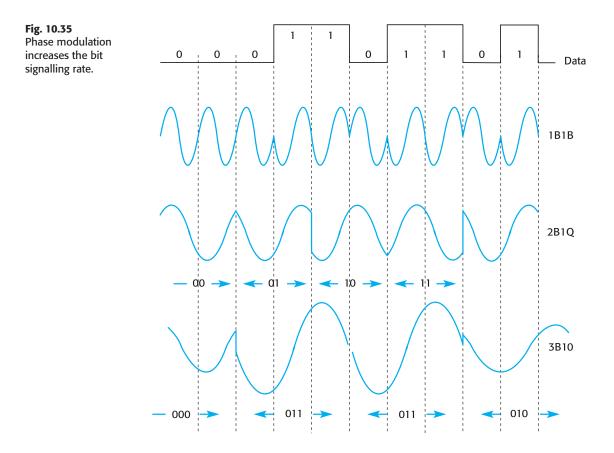

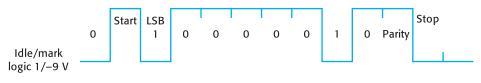

| 10.1 | Serial transmission – data, signals and timing                        | 220 |

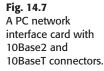

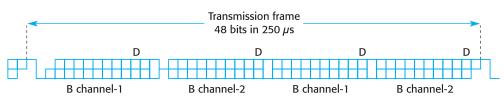

| 10.2 | Data format – encoding techniques                                     | 221 |

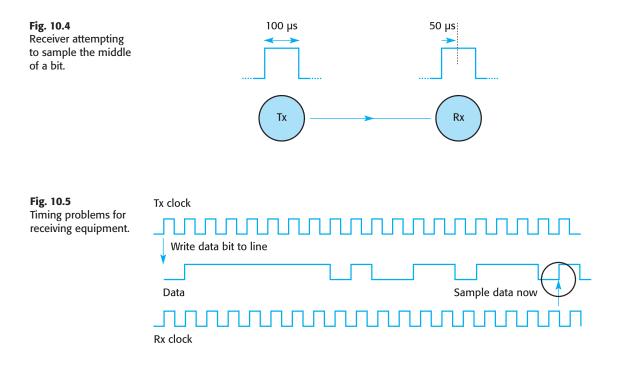

| 10.3 | Timing synchronization – frequency and phase                          | 224 |

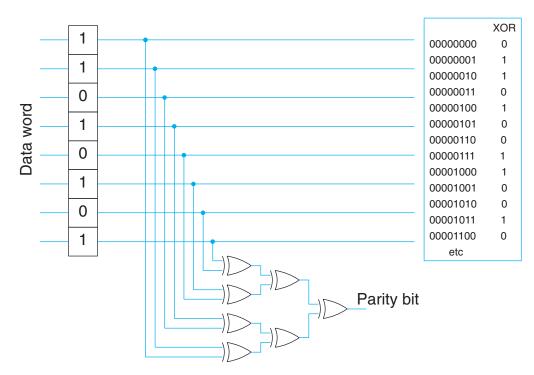

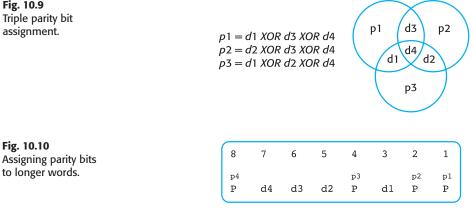

| 10.4 | Data codes and error control – parity, checksums, Hamming codes       |     |

|      | and CRCs                                                              | 227 |

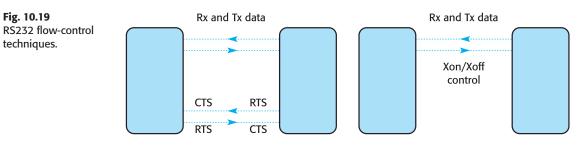

| 10.5 | Flow control – hardware and software methods                          | 235 |

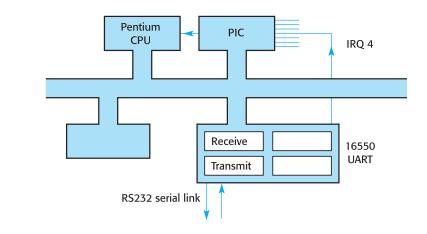

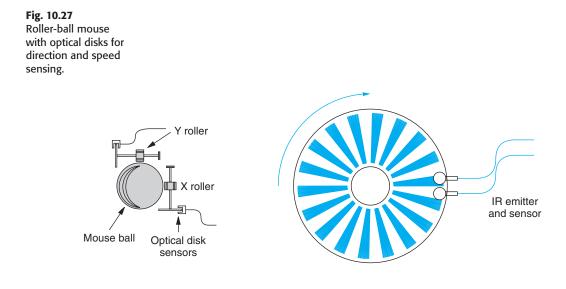

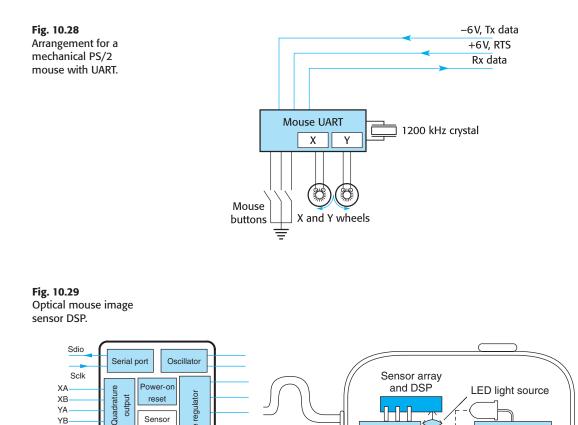

| 10.6<br>10.7<br>10.8 | The 16550 UART – RS232<br>Serial mice – mechanical or optical<br>Serial ports – practical tips, avoiding the frustration | 237<br>244<br>246 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|

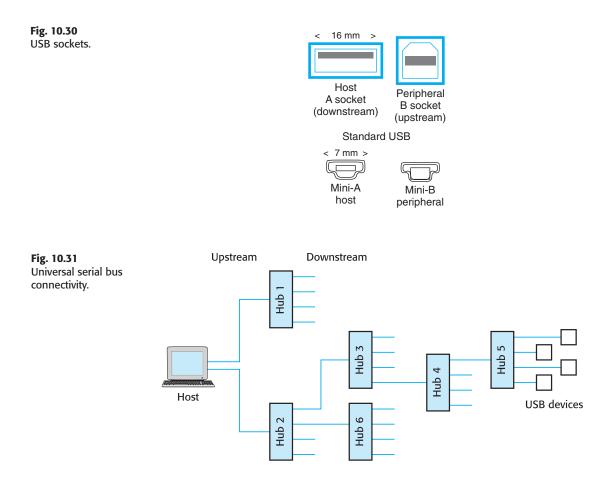

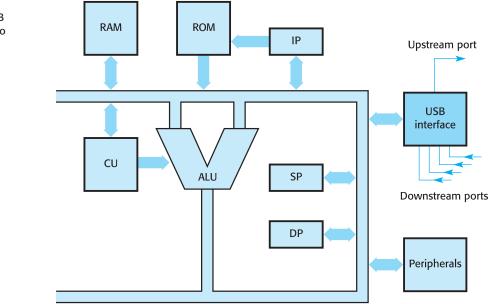

| 10.9                 | USB – Universal Serial Bus                                                                                               | 246               |

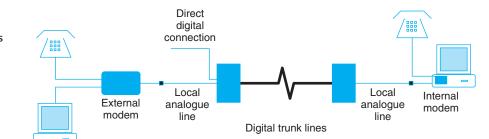

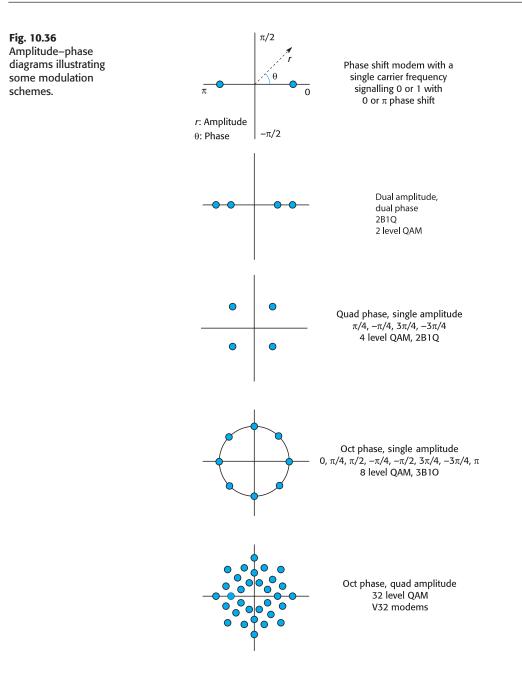

|                      | Modems – modulating carrier waves                                                                                        | 252               |

| 11                   | Parallel connections                                                                                                     | 263               |

| 11.1                 | Parallel interfaces – better performance                                                                                 | 264               |

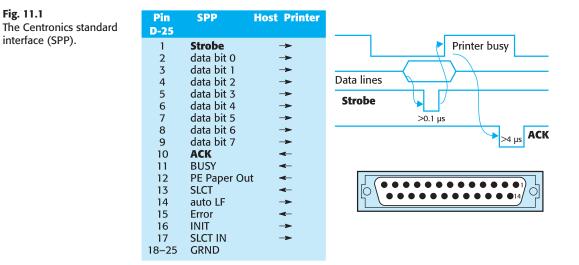

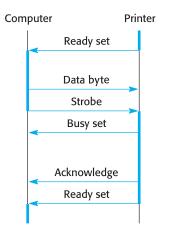

| 11.2                 | Centronics – more than a printer port but less than a bus                                                                | 264               |

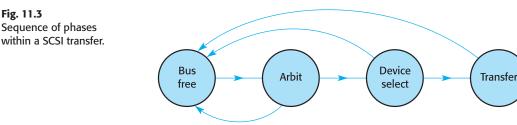

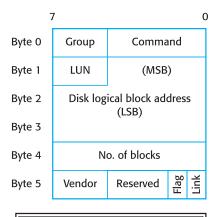

| 11.3                 | SCSI – the Small Computer Systems Interface                                                                              | 267               |

| 11.4                 | IDE – Intelligent Drive Electronics                                                                                      | 271               |

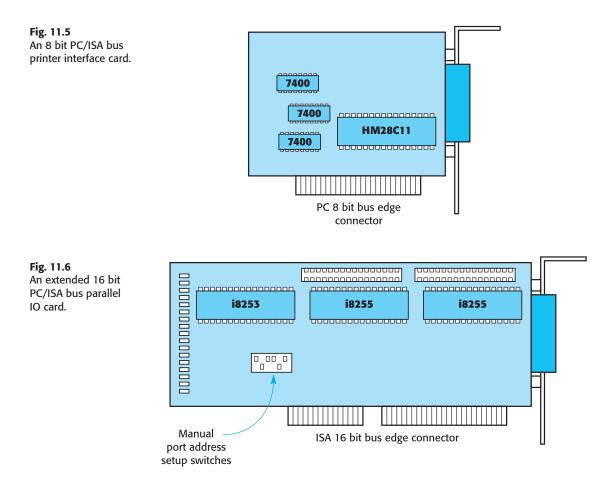

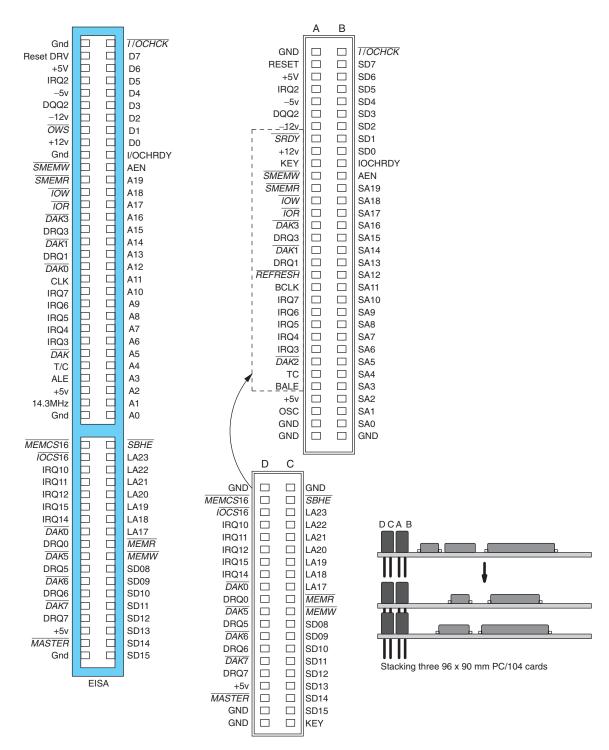

| 11.5                 | AT/ISA – a computer standards success story                                                                              | 272               |

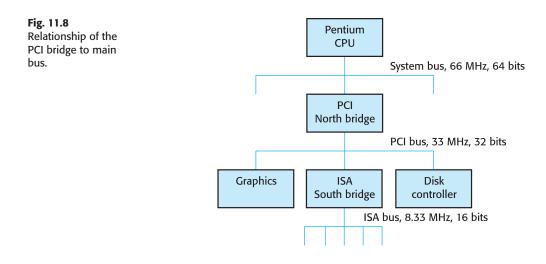

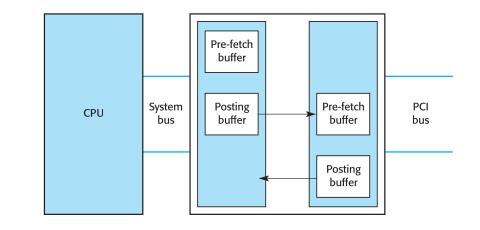

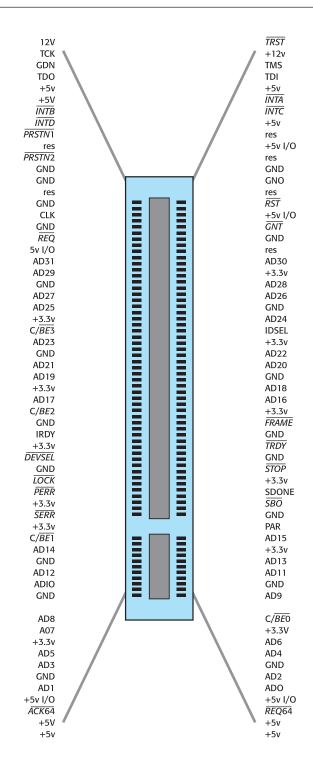

| 11.6                 | PCI – Peripheral Component Interconnection                                                                               | 275               |

| 11.7                 | Plug-and-Play – automatic configuration                                                                                  | 278               |

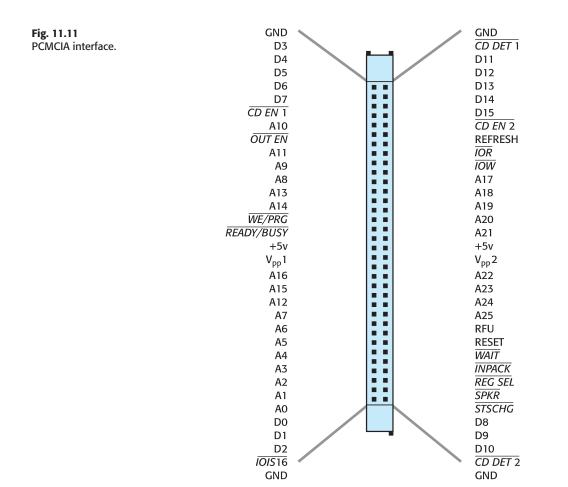

| 11.8                 | PCMCIA – Personal Computer Memory Card                                                                                   |                   |

|                      | International Association                                                                                                | 280               |

|                      |                                                                                                                          |                   |

| 12                   | The memory hierarchy                                                                                                     | 285               |

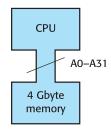

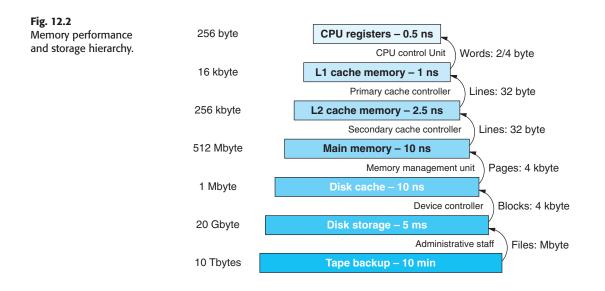

| 12.1                 | Levels of performance – you get what you pay for                                                                         | 286               |

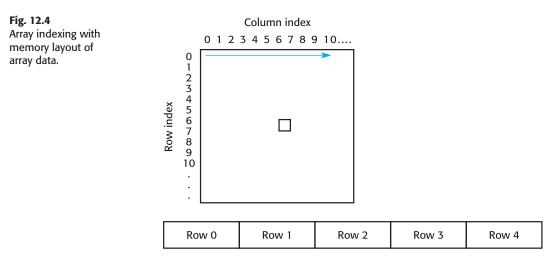

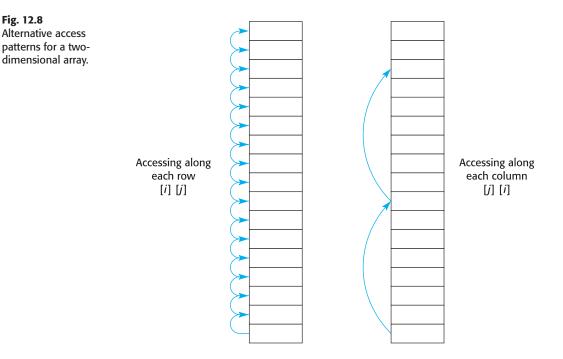

| 12.2                 | Localization of access – exploiting repetition                                                                           | 288               |

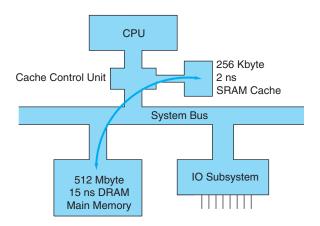

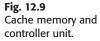

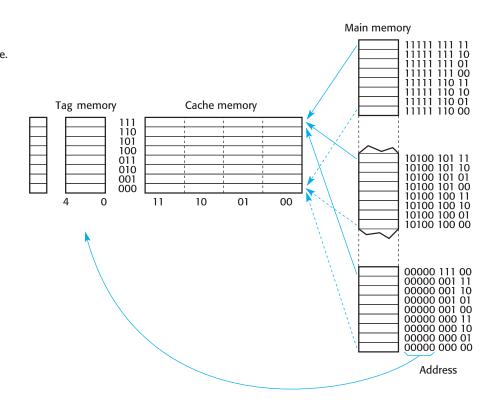

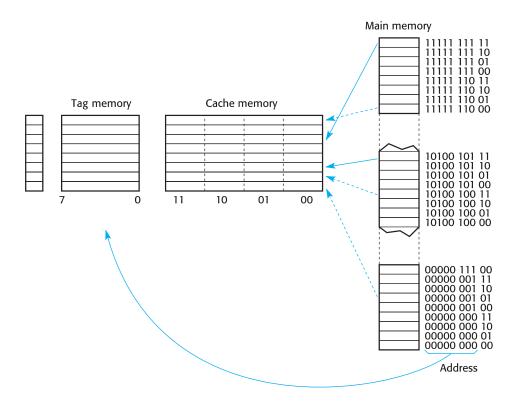

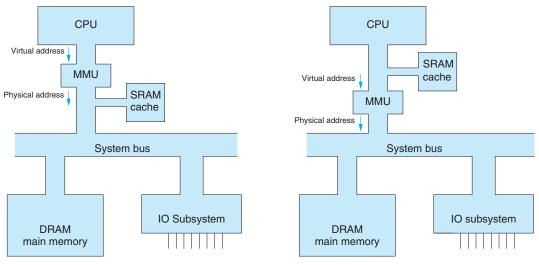

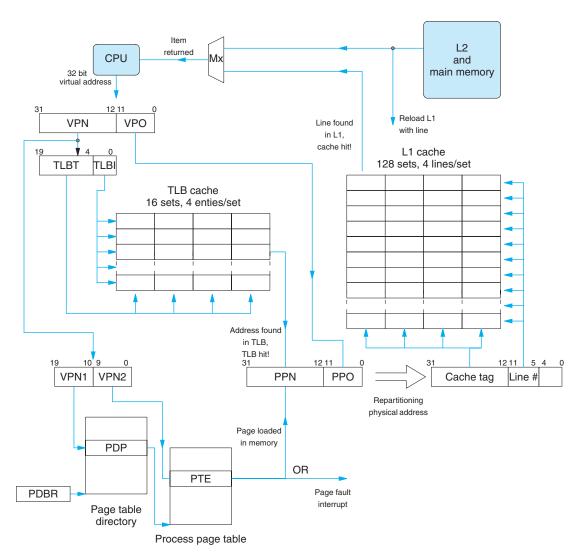

| 12.3                 | Instruction and data caches – matching memory to CPU speed                                                               | 293               |

| 12.4                 | Cache mapping – direct or associative                                                                                    | 295               |

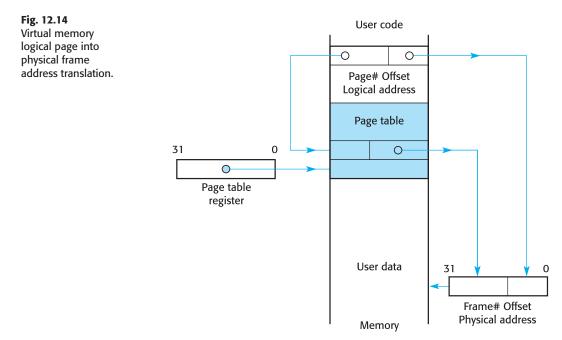

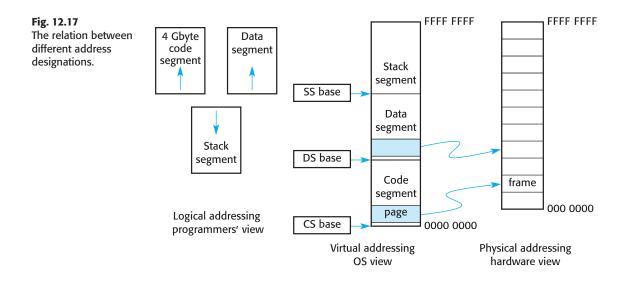

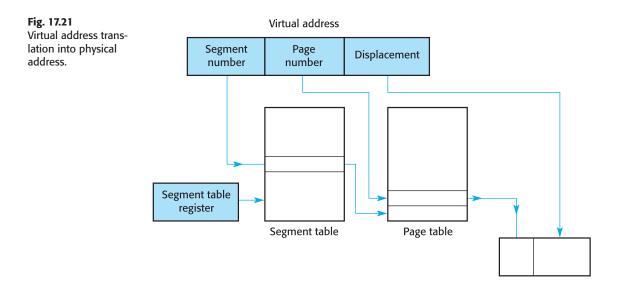

| 12.5                 | Virtual memory – segmentation and demand paging                                                                          | 299               |

| 12.6                 | Address formulation – when, where and how much                                                                           | 304               |

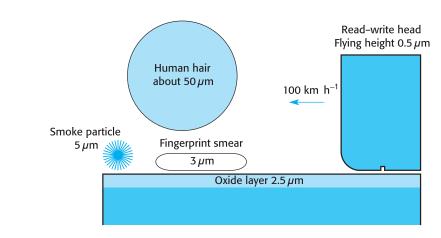

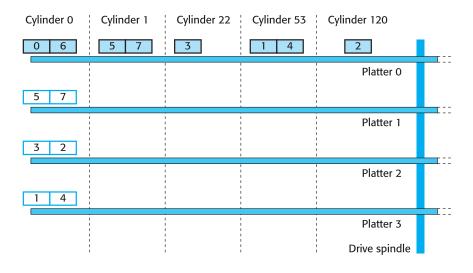

| 12.7                 | Hard disk usage – parameters, access scheduling and                                                                      |                   |

|                      | data arrangement                                                                                                         | 306               |

| 12.8                 | Performance improvement – blocking, caching, defragmentation,                                                            |                   |

| 10.0                 | scheduling, RAM disk                                                                                                     | 310               |

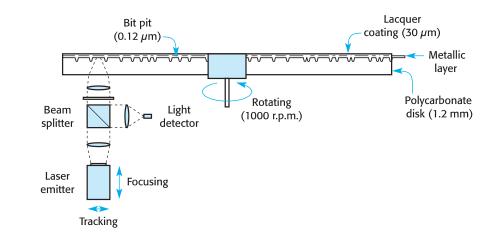

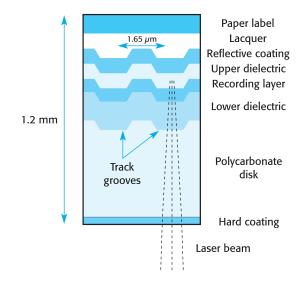

| 12.9                 | Optical discs – CD-DA, CD-ROM, CD-RW and DVDs                                                                            | 312               |

|                      | DVD – Digital Versatile Disc                                                                                             | 316               |

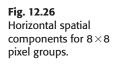

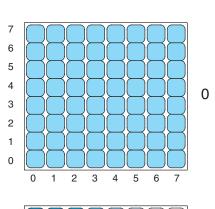

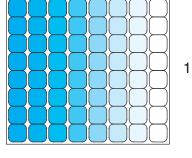

|                      | MPEG – video and audio compression                                                                                       | 316               |

| 12.12                | Flash sticks – the new floppy disk                                                                                       | 323               |

|                      |                                                                                                                          |                   |

|                      |                                                                                                                          |                   |

### Part 2 Networking and increased complexity

| 13 | The programmer's viewpoint                                                   | 329        |

|----|------------------------------------------------------------------------------|------------|

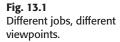

|    | Different viewpoints – different needs<br>Application user – office packages | 330<br>331 |

| 13.3  | Systems administration – software installation and maintenance | 333 |

|-------|----------------------------------------------------------------|-----|

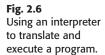

| 13.4  | HLL programmer – working with Java, C++, BASIC or C#           | 337 |

| 13.5  | Systems programming – assembler and C                          | 340 |

| 13.6  | Hardware engineer – design and hardware maintenance            | 344 |

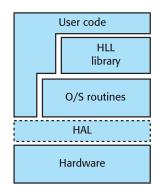

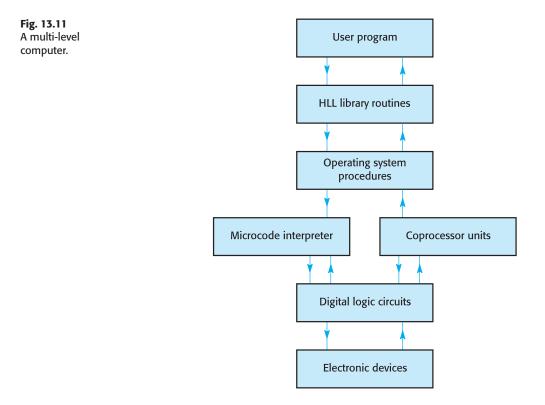

| 13.7  | Layered virtual machines – hierarchical description            | 345 |

| 13.8  | Assemblers – simple translators                                | 346 |

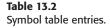

| 13.9  | Compilers – translation and more                               | 347 |

| 14    | Local area networks                                            | 353 |

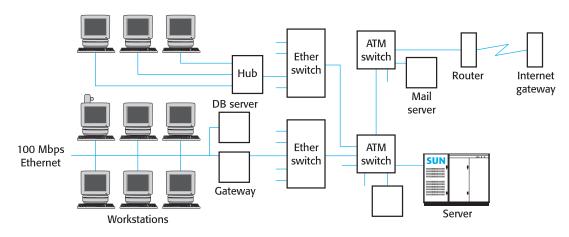

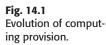

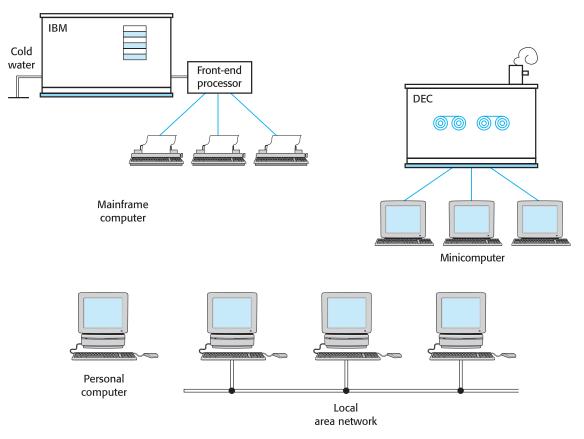

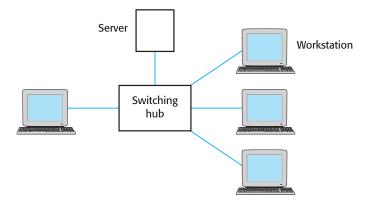

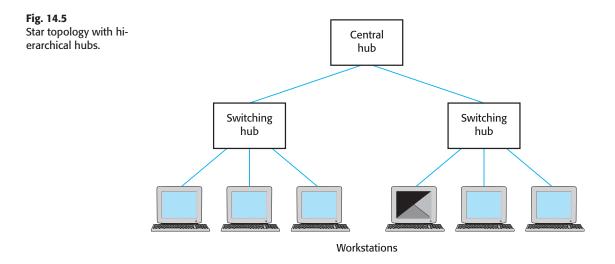

| 14.1  | Reconnecting the users – email, printers and database          | 354 |

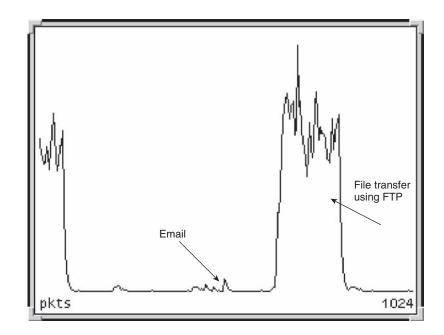

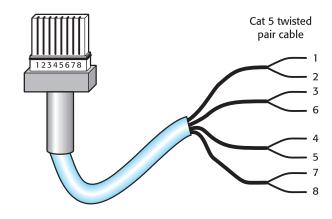

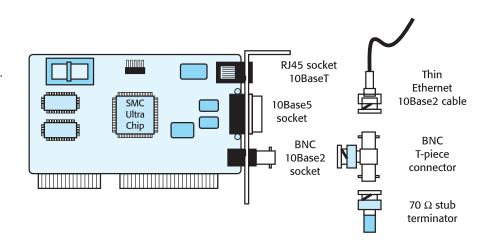

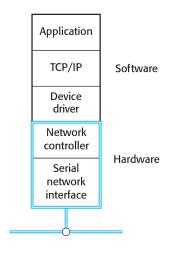

| 14.2  | PC network interface – cabling and interface card              | 359 |

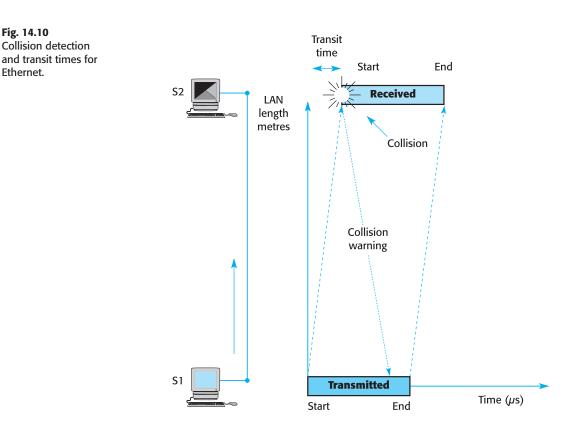

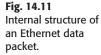

| 14.3  | Ethernet – Carrier Sense, Multiple Access/Collision Detect     | 363 |

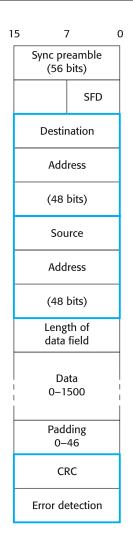

| 14.4  | LAN addressing – logical and physical schemes                  | 367 |

| 14.5  | Host names – another layer of translation                      | 370 |

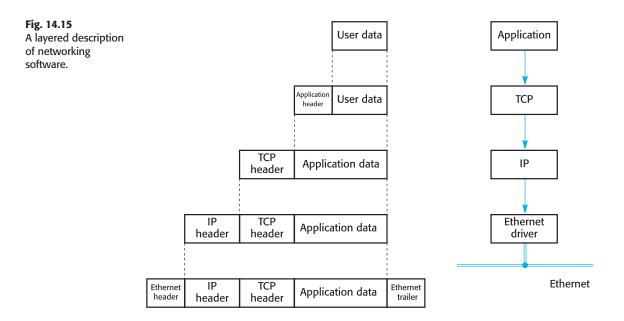

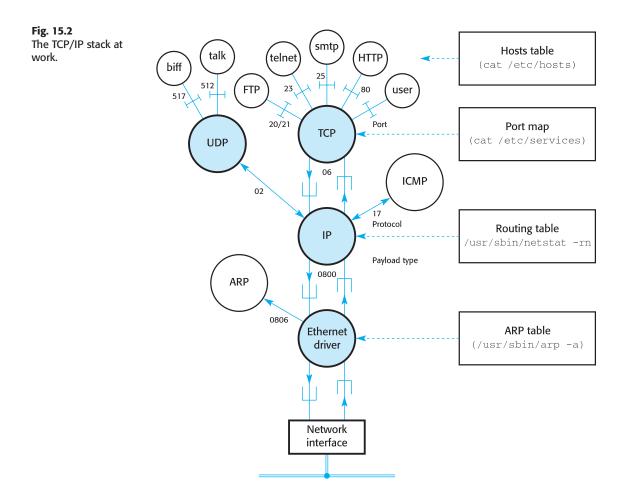

| 14.6  | Layering and encapsulation – TCP/IP software stack             | 371 |

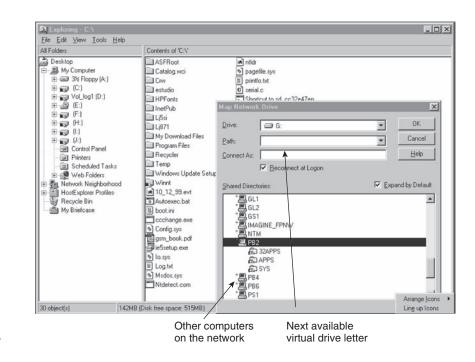

| 14.7  | Networked file systems – sharing files across a network        | 372 |

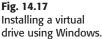

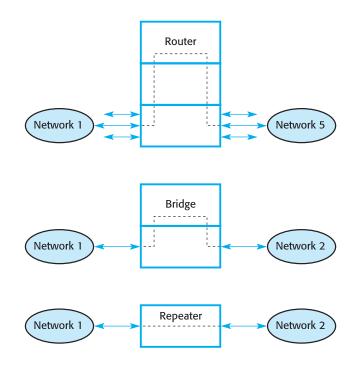

| 14.8  | Interconnecting networks – gateways                            | 374 |

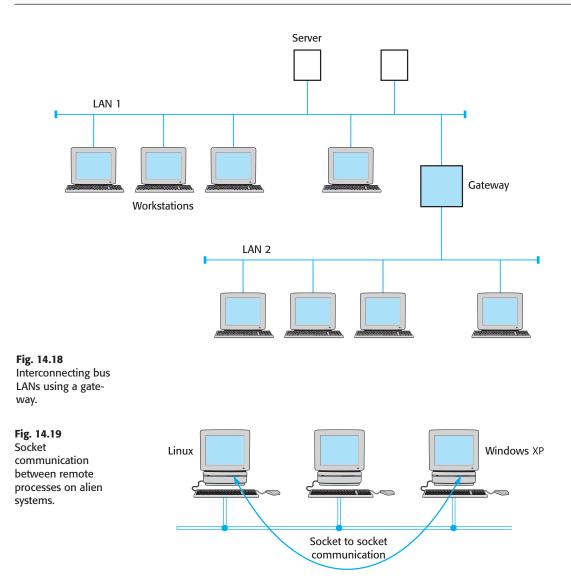

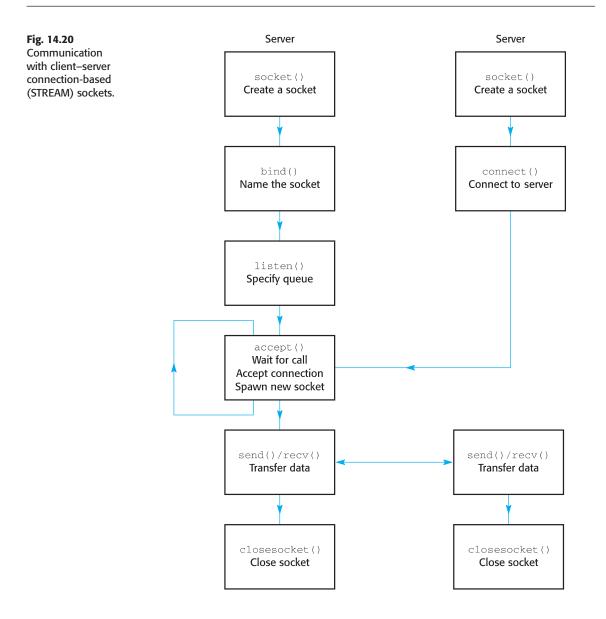

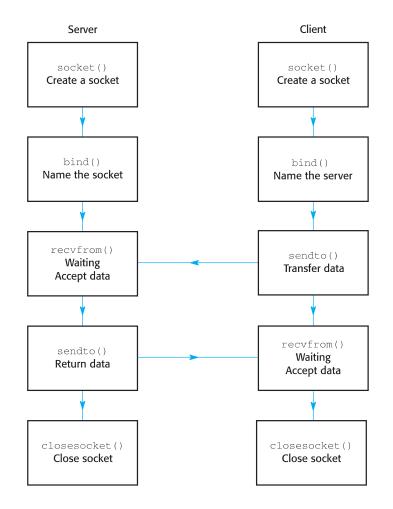

| 14.9  | Socket programming – an introduction to WinSock                | 374 |

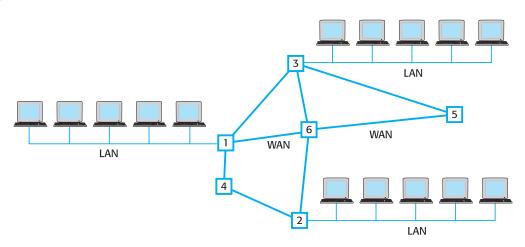

| 15    | Wide area networks                                             | 383 |

| 15.1  | The Internet – origins                                         | 384 |

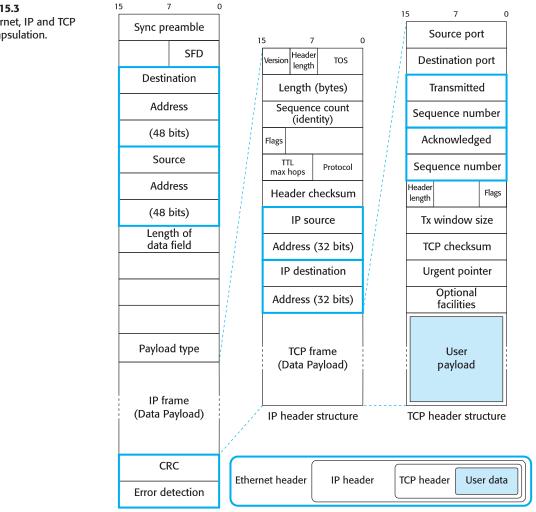

| 15.2  | TCP/IP – the essential protocols                               | 386 |

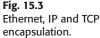

| 15.3  | TCP – handling errors and flow control                         | 390 |

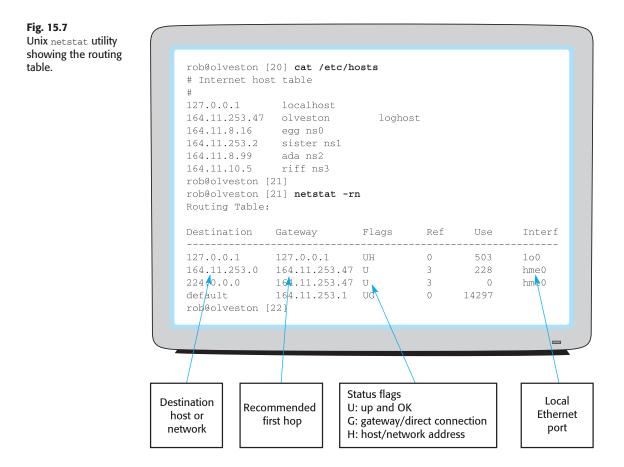

| 15.4  | IP routing – how packets find their way                        | 392 |

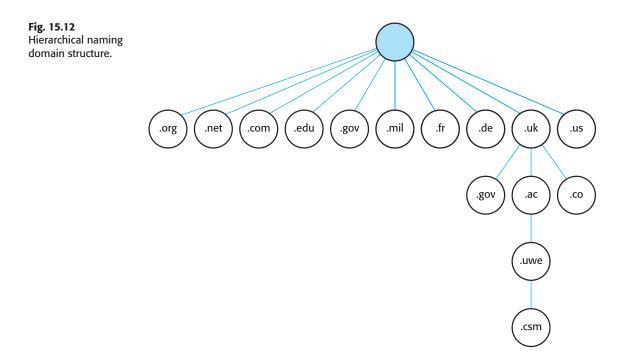

| 15.5  | DNS – Distributed Name Database                                | 398 |

| 15.6  | World Wide Web – the start                                     | 401 |

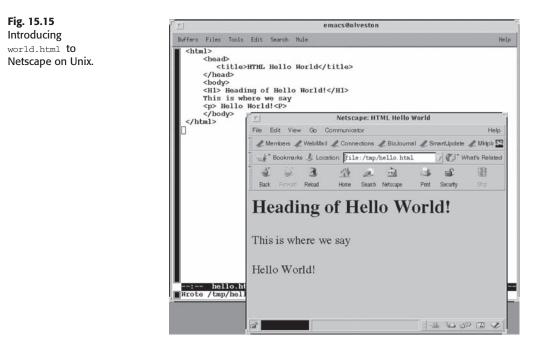

| 15.7  | Browsing the Web – Netscape Navigator                          | 403 |

| 15.8  | HTTP – another protocol                                        | 407 |

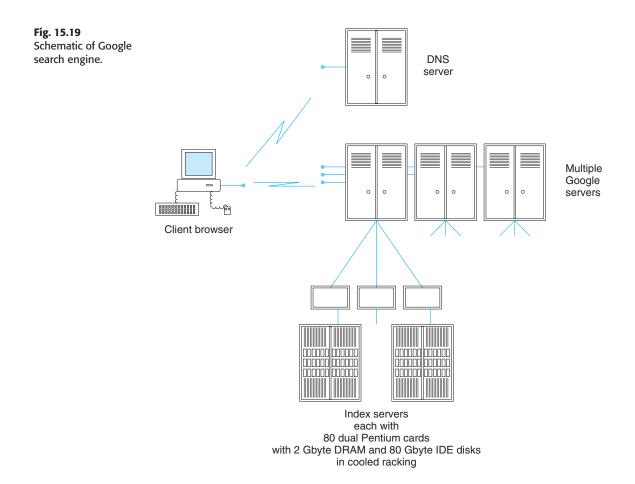

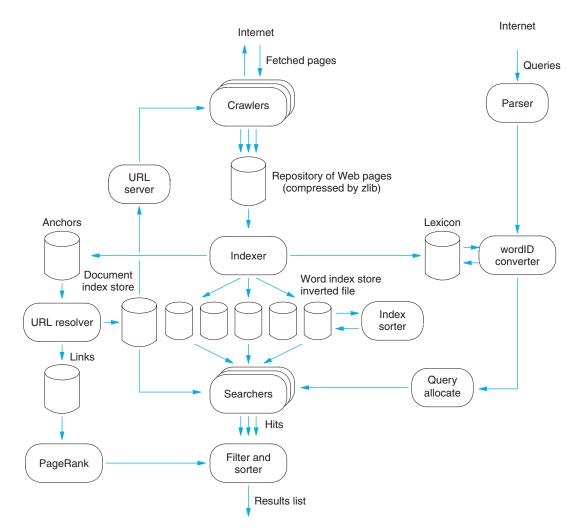

| 15.9  | Search engines – Google                                        | 409 |

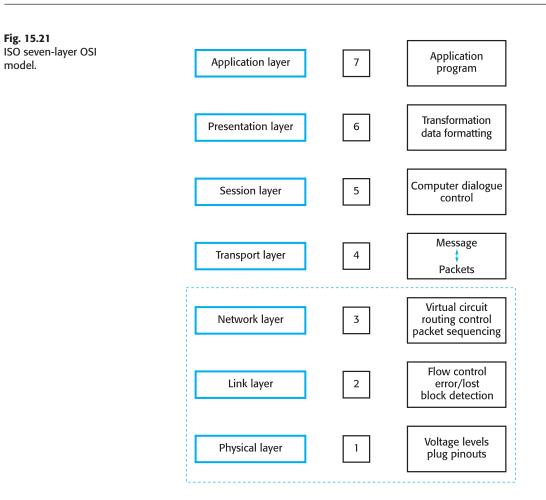

| 15.10 | Open Systems Interconnect – an idealized scheme                | 412 |

| 16    | Other networks                                                 | 419 |

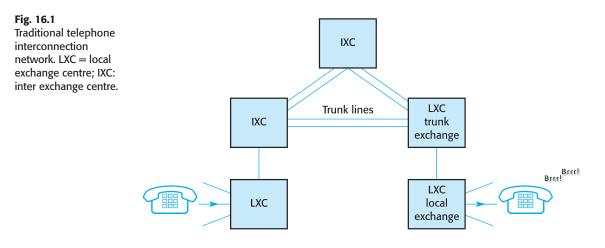

| 16.1  | The PSTN – telephones                                          | 420 |

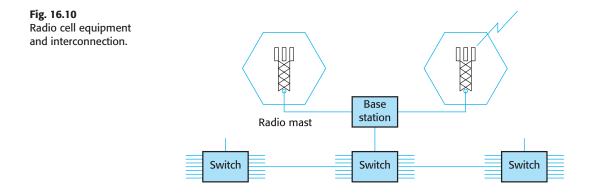

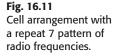

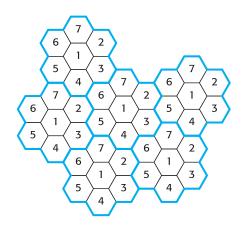

| 16.2  | Cellnets – providers of mobile communications                  | 426 |

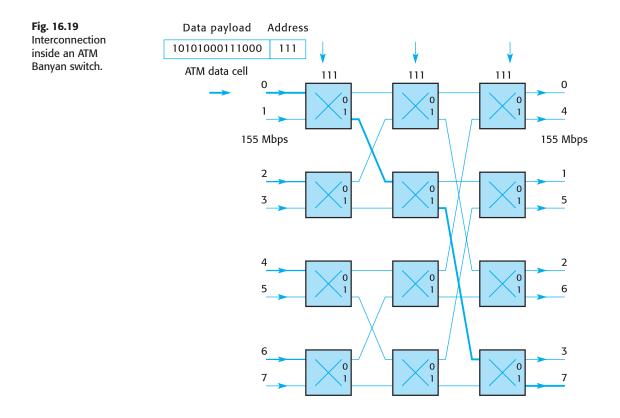

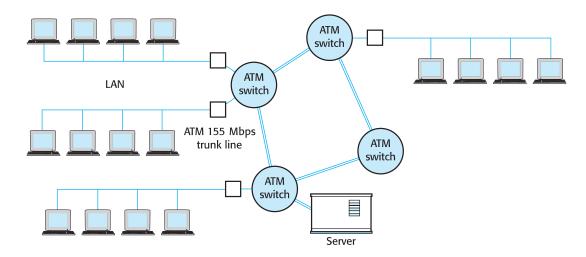

| 16.3  | ATM – Asynchronous Transfer Mode                               | 435 |

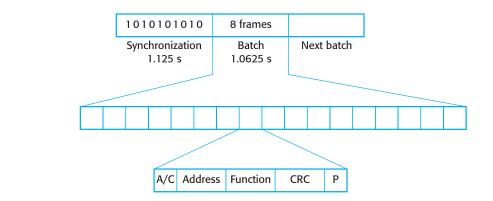

| 16.4  | Messaging – radio paging and packet radio networks             | 440 |

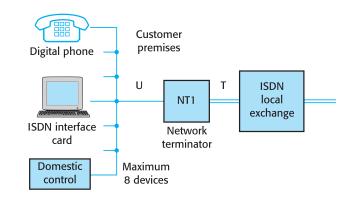

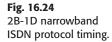

| 16.5  | ISDN – totally digital                                         | 442 |

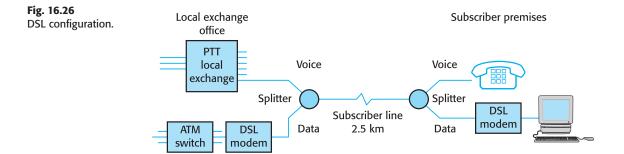

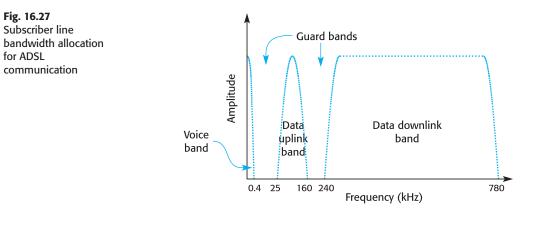

| 16.6  | DSL – Digital Subscriber Line                                  | 446 |

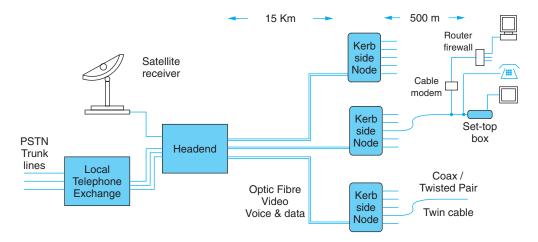

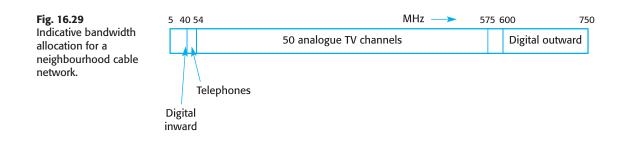

| 16.7  | Cable television – facilities for data transmission            | 447 |

| 17    | Introduction to operating systems                                                           | 455   |

|-------|---------------------------------------------------------------------------------------------|-------|

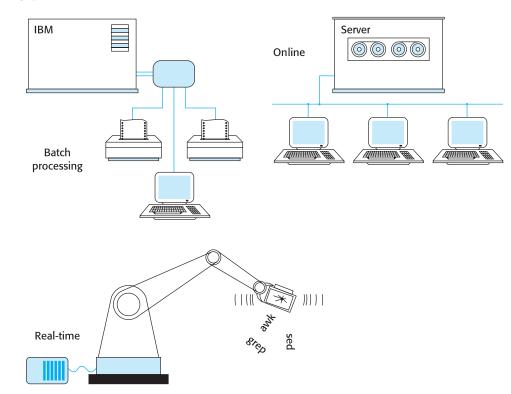

| 17.1  | Historic origins – development of basic functions                                           | 456   |

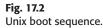

| 17.2  | Unix – a landmark operating system                                                          | 459   |

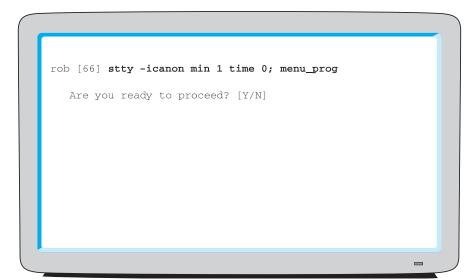

| 17.3  | Outline structure – modularization                                                          | 462   |

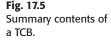

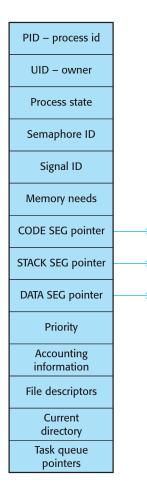

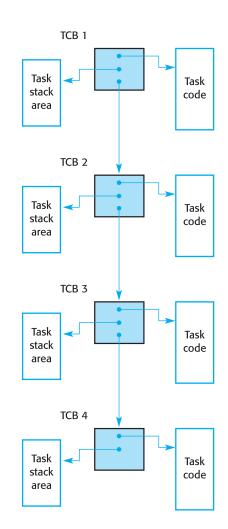

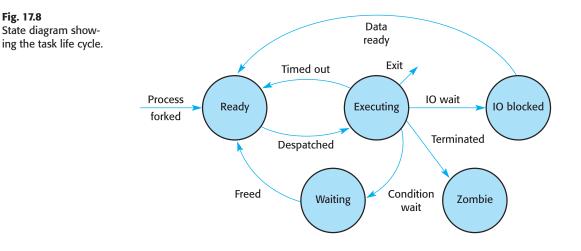

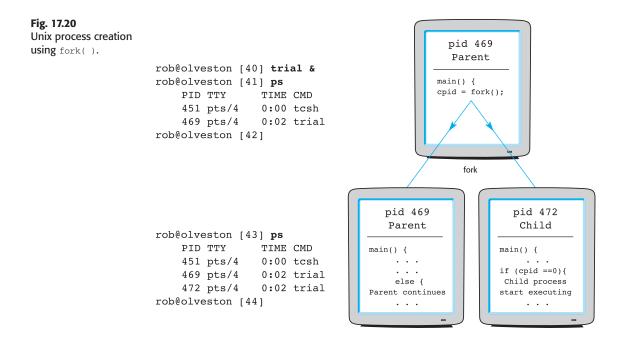

| 17.4  | Process management – initialization and dispatching                                         | 463   |

| 17.5  | Scheduling decisions – time-slicing, demand preemption                                      |       |

|       | or cooperative                                                                              | 469   |

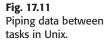

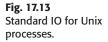

| 17.6  | Task communication – pipes and redirection                                                  | 471   |

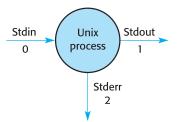

| 17.7  | Exclusion and synchronization – semaphores and signals                                      | 473   |

| 17.8  | Memory allocation - malloc() and free()                                                     | 479   |

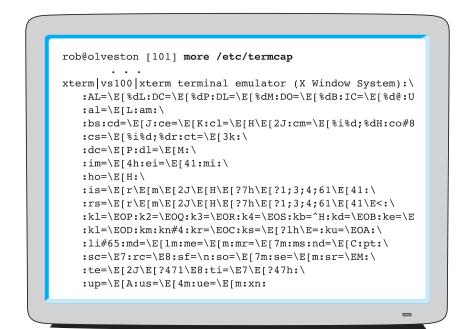

| 17.9  | User interface – GUIs and shells                                                            | 481   |

| 17.10 | Input–output management – device handlers                                                   | 482   |

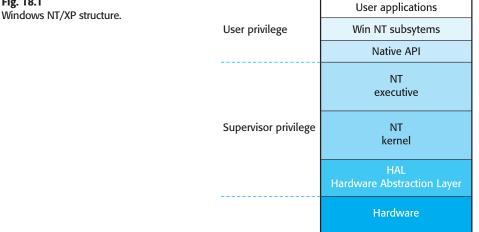

| 18    | Windows XP                                                                                  | 491   |

| 18.1  | Windows GUIs – responding to a need                                                         | 492   |

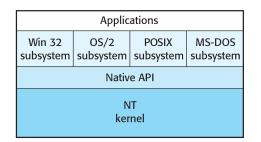

| 18.2  | Win32 – the preferred user API                                                              | 494   |

| 18.3  | Processes and threads – multitasking                                                        | 495   |

| 18.4  | Memory management – virtual memory implementation                                           | 496   |

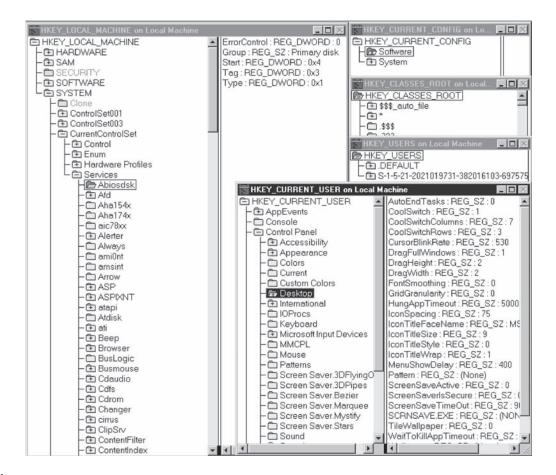

| 18.5  | Windows Registry – centralized administrative database                                      | 496   |

| 18.6  | NTFS – Windows NT File System                                                               | 498   |

| 18.7  | File access – ACLs, permissions and security                                                | 499   |

| 18.8  | Sharing software components – OLE, DDE and COM                                              | 502   |

| 18.9  | Windows NT as a mainframe – Winframe terminal server                                        | 502   |

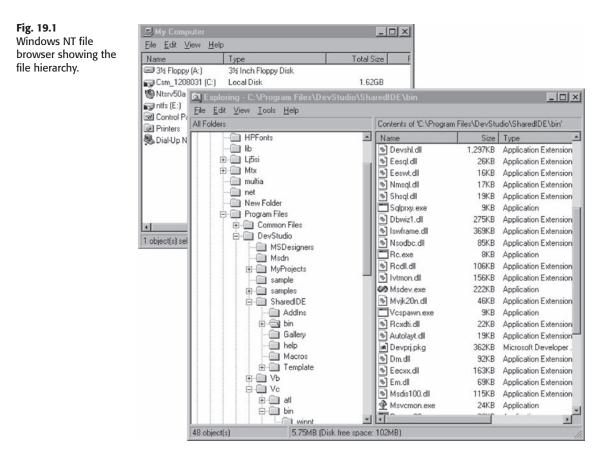

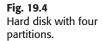

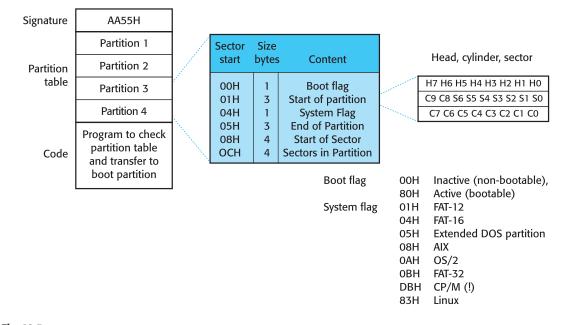

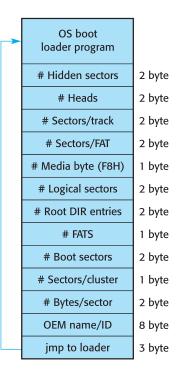

| 19    | Filing systems                                                                              | 507   |

| 19.1  | Data storage – file systems and databases                                                   | 508   |

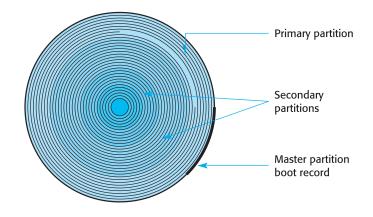

| 19.2  | The PC file allocation table – FAT                                                          | 515   |

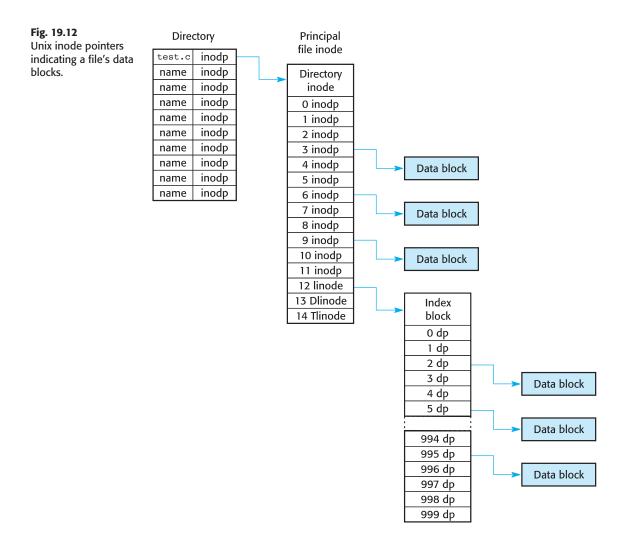

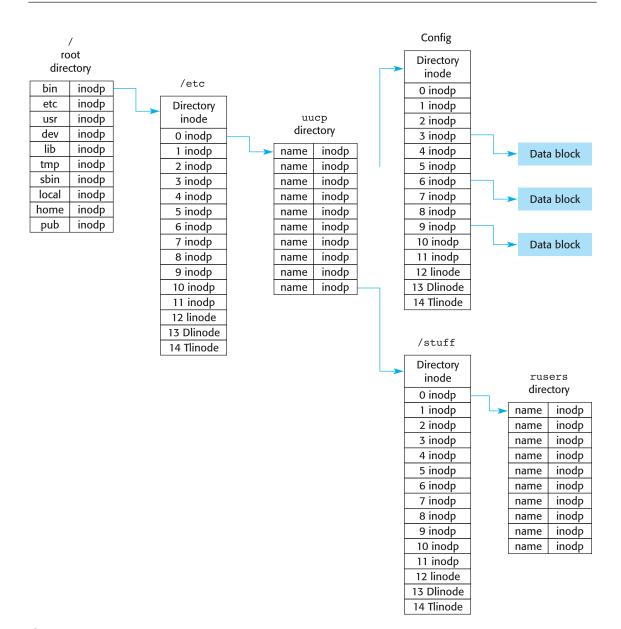

| 19.3  | Unix inodes – they do it differently                                                        | 518   |

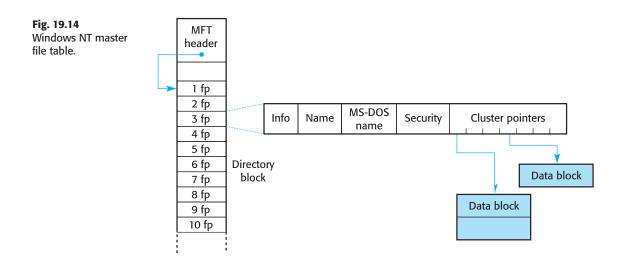

| 19.4  | Microsoft NTFS – complexity and security                                                    | 523   |

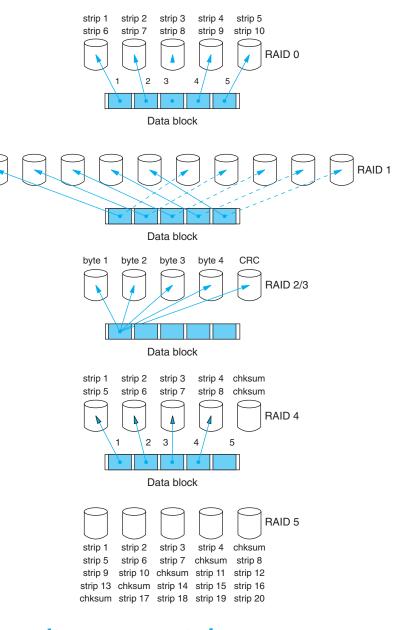

| 19.5  | RAID configuration – more security for the disk subsystem                                   | 525   |

| 19.6  | File security – access controls                                                             | 526   |

| 19.7  | CD portable file system – multi-session contents lists                                      | 528   |

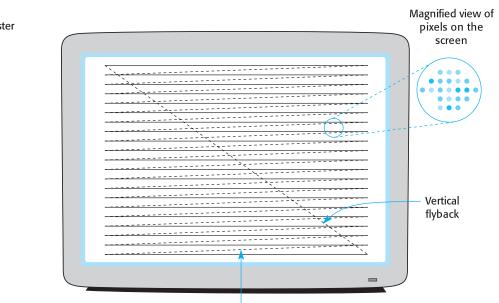

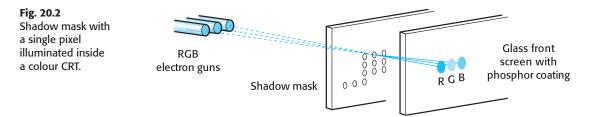

| 20    | Visual output                                                                               | 533   |

| 20    |                                                                                             | 555   |

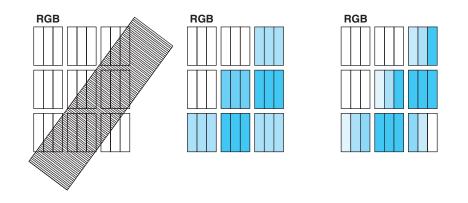

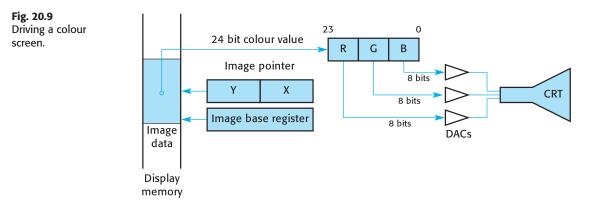

| 20.1  | Computers and graphics – capture, storage, processing                                       | F 7 4 |

| 20.2  | and redisplay                                                                               | 534   |

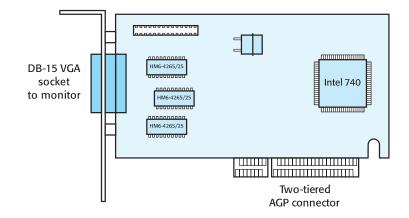

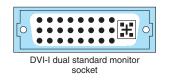

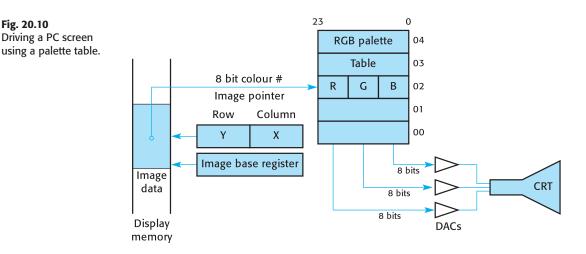

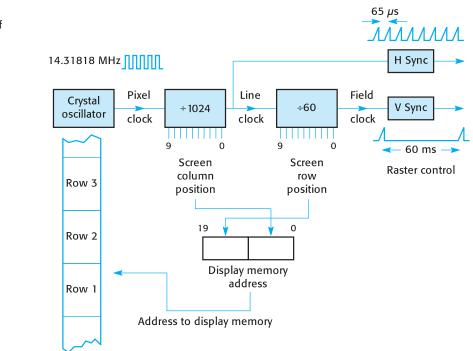

| 20.2  | PC graphics adapter cards – graphics coprocessors<br>Laser printers – this is mechatronics! | 541   |

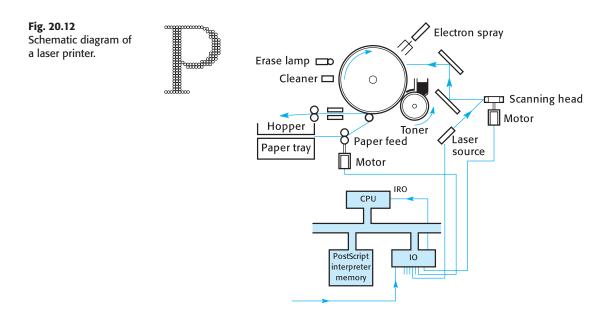

| 20.3  |                                                                                             | 547   |

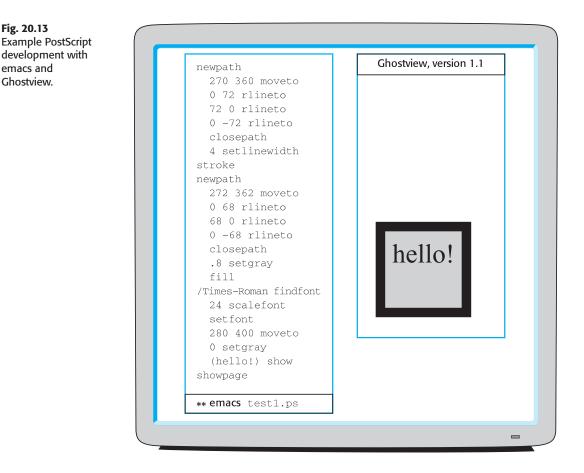

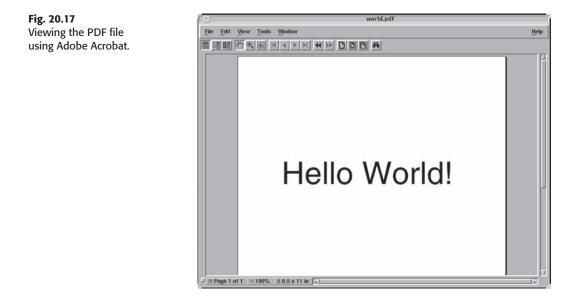

| 20.4  | Adobe PostScript – a page description language                                              | 549   |

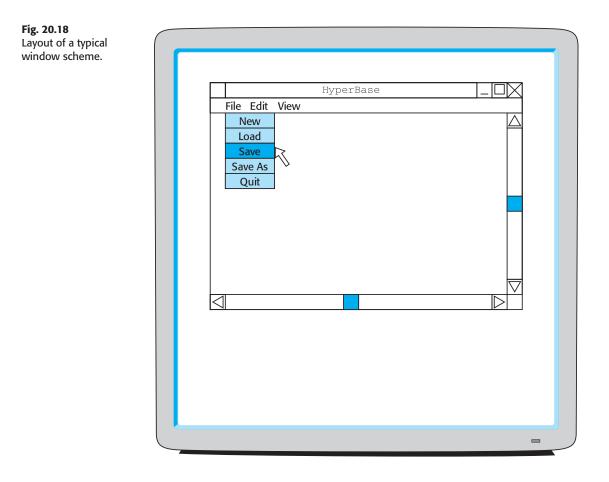

| 20.5  | WIMPs – remodelling the computer                                                            | 554   |

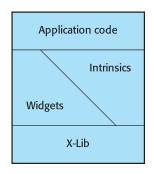

| 20.6<br>20.7<br>20.8                         | Win32 – graphical API and more<br>The X Window system – enabling distributed processing<br>MMX technology – assisting graphical calculations                                                                                                                                                                                                                                                                                                                                                                                                                      | 555<br>557<br>558                                                                |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 21                                           | RISC processors: ARM and SPARC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 563                                                                              |

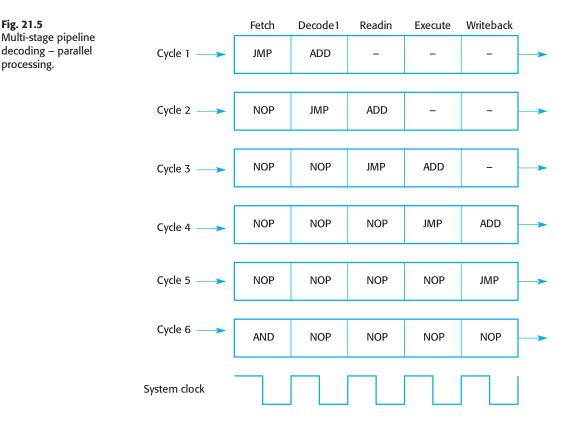

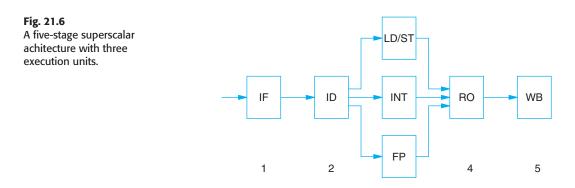

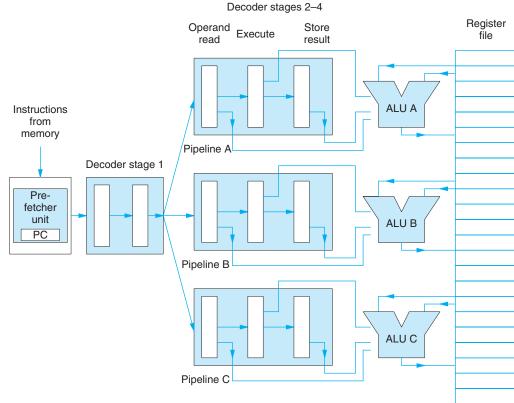

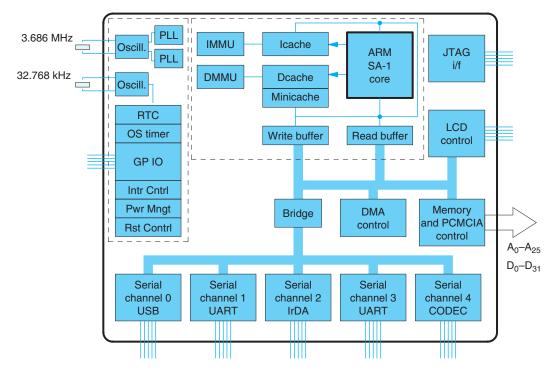

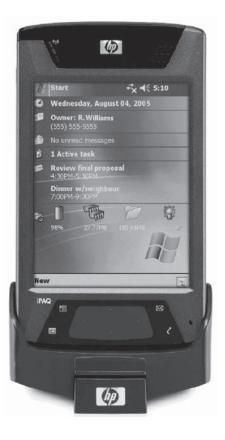

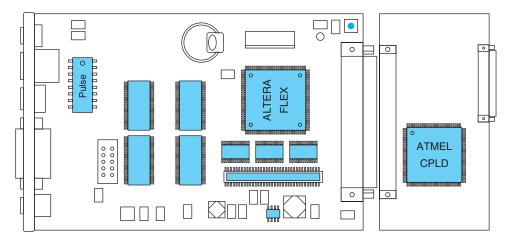

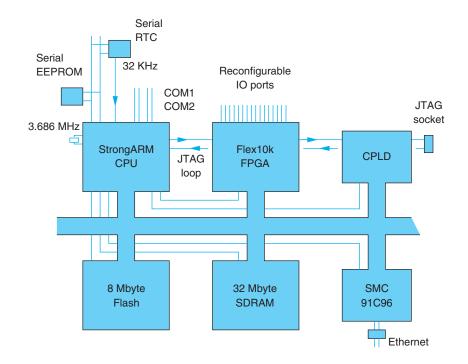

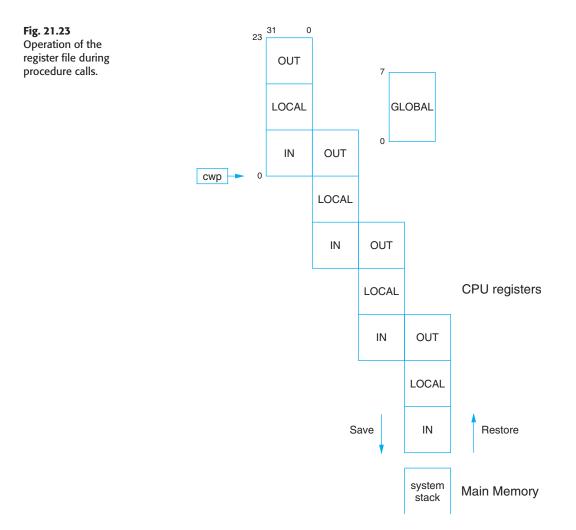

| 21.11                                        | Justifying RISC – increased instruction throughput<br>Pipeline techniques – more parallel operations<br>Superscalar methods – parallel parallelism<br>Register files – many more CPU registers<br>Branch prediction methods – maintaining the pipelines<br>Compiler support – an essential part of RISC<br>The ARM 32 bit CPU – origins<br>StrongARM processor – a 32 bit microcontroller<br>The HP iPAQ – a StrongARM PDA<br>Puppeteer – a StrongARM SBC<br>Sun SPARC – scalar processor architecture as RISC<br>Embedded systems – cross-development techniques | 564<br>569<br>571<br>572<br>574<br>576<br>576<br>585<br>588<br>590<br>592<br>594 |

| 22                                           | VLIW processors: the EPIC Itanium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 601                                                                              |

| 22.1<br>22.2<br>22.3<br>22.4                 | Itanium 64 bit processor – introduction<br>Itanium assembler – increasing the control of the CPU<br>Run-time debugging – gvd/gdb<br>Future processor design – debate                                                                                                                                                                                                                                                                                                                                                                                              | 602<br>609<br>613<br>615                                                         |

| 23                                           | Parallel processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 619                                                                              |

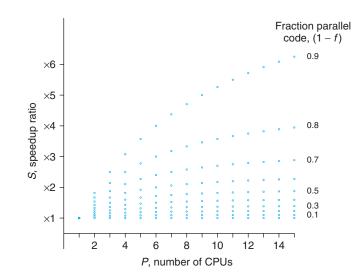

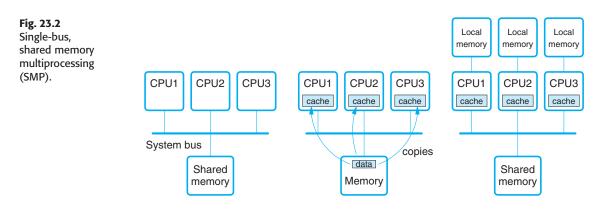

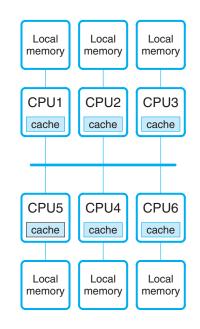

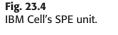

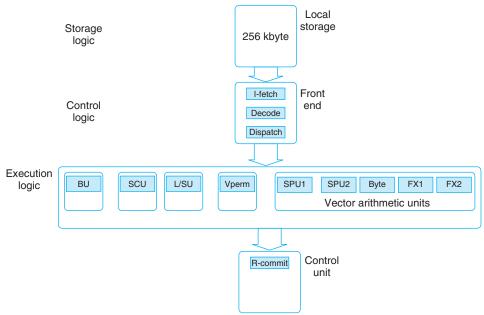

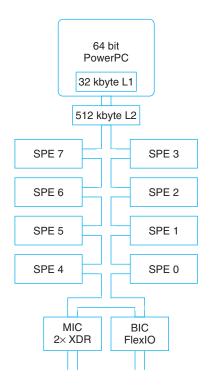

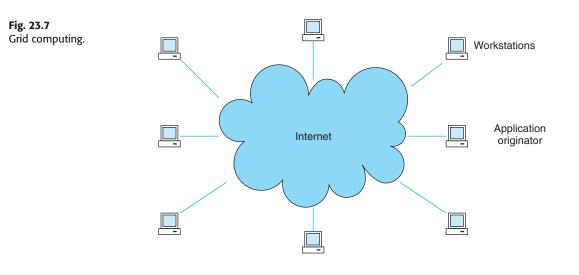

| 23.1<br>23.2<br>23.3<br>23.4<br>23.5<br>23.6 | Parallel processing – the basis<br>Instruction-level parallelism (ILP) – pipelining<br>Superscalar – multiple execution units<br>Symmetric, shared memory multiprocessing (SMP) – the future?<br>Single-chip multiprocessors – the IBM Cell<br>Clusters and grids – application-level parallelism                                                                                                                                                                                                                                                                 | 620<br>623<br>623<br>623<br>626<br>629                                           |

|                                              | Appendix: MS Visual Studio 8, Express Edition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 635                                                                              |

|                                              | Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 647                                                                              |

|                                              | Answers to end-of-chapter questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 661                                                                              |

|                                              | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 713                                                                              |

|                                              | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 717                                                                              |

#### Supporting resources

Visit www.pearsoned.co.uk/williams to find valuable online resources

#### **Companion Website for students**

- Slides and handouts for each chapter

- Laboratory worksheets

- Example scripts for class phase tests

#### For instructors

• Answers to test questions

For more information please contact your local Pearson Education sales representative or visit www.pearsoned.co.uk/williams

## Preface

Writing a textbook for a subject area such as computing which changes so rapidly is a frightening experience. For this Second Edition, there was a temptation simply to create a find-and-replace editing macro which would update all numeric parameters by inserting or deleting the extra zero as appropriate! Although fundamental technical principles do not change so rapidly, it is very important to maintain a clear grasp of the speed of current processors and their likely memory size. Appreciating the possible download capacity of a broadband link can also be useful. When we estimate something, it is a valuable skill to be able to say immediately if the result is 'common sense reasonable', or plain daft. All scientists and engineers practise this skill, and so should programmers. I do remember once contributing to the loss of a commercial contract when an estimate of 6 hours for a file transfer was accepted at board level. Only later did I realize that I had forgotten to divide the number by 10, to account for Bytes/s instead of bits/s.

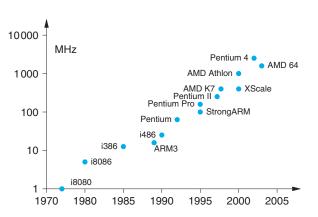

In this new edition, Intel's 64 bit Itanium processor has been given more space in a separate chapter because it is considered to represent a key new architecture for the post-RISC era. The terms RISC and post-RISC are used to distinguish more clearly between the original vision of simple, fast processors and their recent, more complex successors. The ARM CPU has been adopted as the example architecture for a micro-controller, using the Intel StrongARM/XScale for practical examples. More description and explanation about USB communications has also been included to reflect its growing relevance to programmers and computer users. The technology of modems has been updated to include 56k dialup and ADSL broadband equipment. The wide enthusiasm for portable devices dependent on audio and video compression techniques has stimulated a new section introducing MPEG algorithms. The sections dealing with the WWW and search engines have been overhauled and updated, using Google as the principal example.

A new chapter introducing parallel, cluster and grid configurations has been included with mention of the novel IBM Cell processor which is destined to revitalize the games console industry and, perhaps, revolutionize desktop computing.

Preparing for a new edition offers the opportunity to remove all those pernicious mistakes which somehow hang on against all our best efforts. But unfortunately it also allows for the introduction of a fresh set of errors, for which I must immediately accept the blame. I have, however, learnt the bright side of such mistakes, which is the rash of charming emails that I have received from around the world pointing out, in mostly very apologetic tones, the errors. Thanks again to those who took the trouble to get in touch with me.

I must also acknowledge the major contribution of the two commissioning editors, Keith Mansfield, for the first edition, and Simon Plumtree for the second. Without their encouragement and efforts the text would have languished on my hard disk as a troff/pic file.

# Preface to the first edition

#### Origins of this book

This book is based on a first-year degree course called Computer Systems Architecture (uqc104s1), which I have delivered for some years at the University of the West of England (UWE), Bristol. The course has expanded, contracted and expanded again, so it has been thoroughly shaken about and reorganized several times. Many of our graduates are recruited into the growing telecommunications industry, and interest in this subject area is very high. Therefore the course, and this book, reflect the shift in interest to encompass not only applied computer science but also data communication and networking.

#### Students

Whereas ten years ago students came into our first year with little in the way of computing qualifications or experience, now over half our new students have already successfully completed a two-year course (A level or BTEC) in the computing field. They have enrolled on a degree course in BSc Computer Science, BSc Software Engineering or BSc Computing for Real-Time Systems. The latter, in particular, attracts technical enthusiasts who are keen to progress into exciting new subject areas such as networking, Unix, embedded systems or real-time programming. With this more demanding audience in mind, I have attempted to inject new ideas and pursue fresh directions. The danger is always that such students will become bored and withdraw their commitment if they consider the course to be 'too easy' or 'out of date'. This book attempts to acknowledge and build on their existing experience.

Another worry often voiced by students concerns the place of mathematics within the course. Well, no advanced mathematics is needed. You will only occasionally be asked to use simple algebra and arithmetic. Common sense will be your most valuable resource! Also, we will do no soldering. This is not an electronics course.

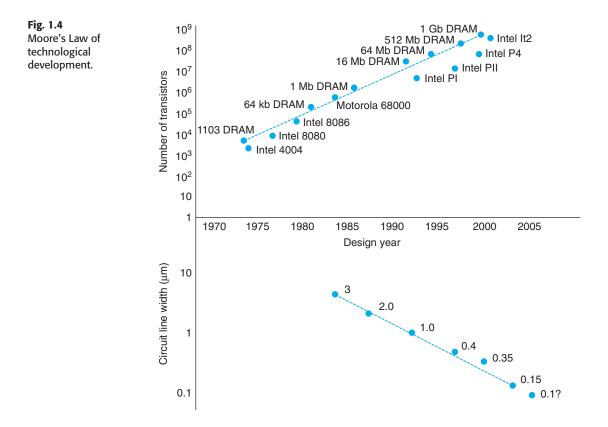

#### Technological change

Keeping pace with technological change is an issue for all computing courses and texts, and I have taken up this challenge by basing the book on the Pentium processor, despite its daunting complexity. Systems which seemed capable of holding their advanced position within the market-place for several years, are now overtaken within months of launch. Software tools are being developed and adopted by commercial programmers long before universities have had a chance

to obtain a copy. As a result, computing curricula are in need of continuous review in order to maintain their currency within the wider context. It is not uncommon for my students to return home to use their own computer systems because they are more advanced than those available in our undergraduate laboratories! But it is worrying to me how fashion-conscious the computing field has become. This can lead to rapid demotivation when the ideas and examples discussed during lectures, although academically and intellectually valid, are perceived as outdated. In this regard, I hope to have included enough contemporary material to maintain your interest!

#### Use of this text

We all learn differently, but the ability to use text effectively has been at the core of modern civilization for a long time. We all benefit so much from people's experience recorded on paper for others to read. Ignoring this vast resource is deliberately handicapping yourself. Life is difficult enough without conceding an unnecessary penalty! If anything, the introduction of the WWW has placed even greater literacy demands on everyone. Most Web pages presenting useful information still depend heavily on text. A picture may be worth a thousand words, but it is often the accompanying text that gives you a first glimmer of understanding.

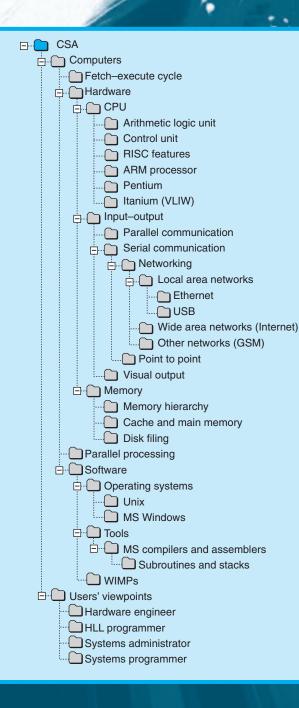

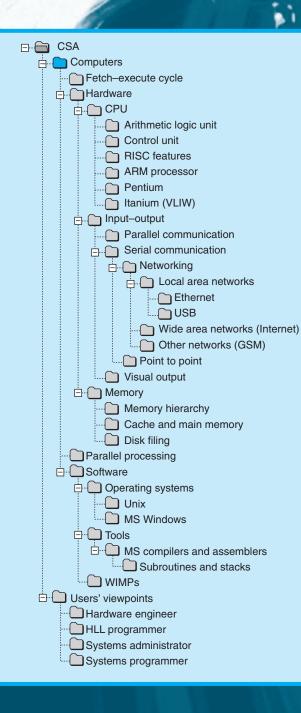

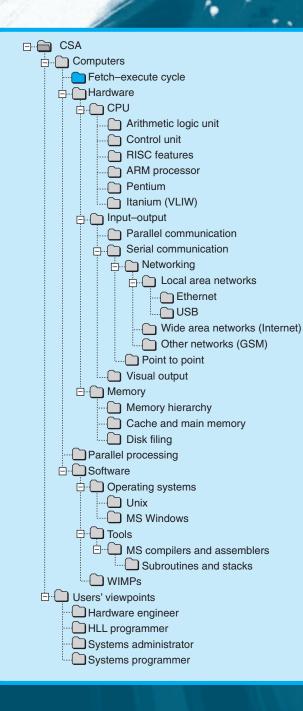

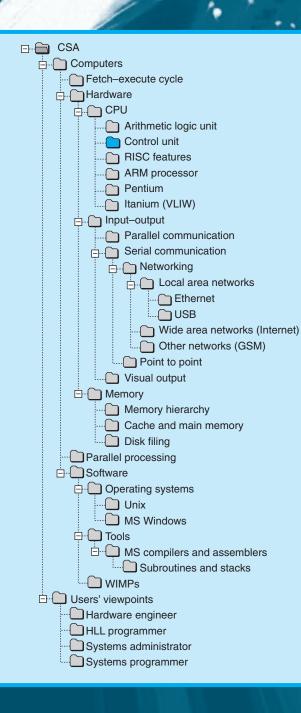

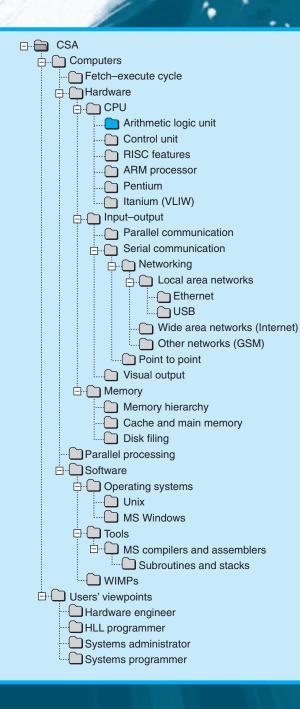

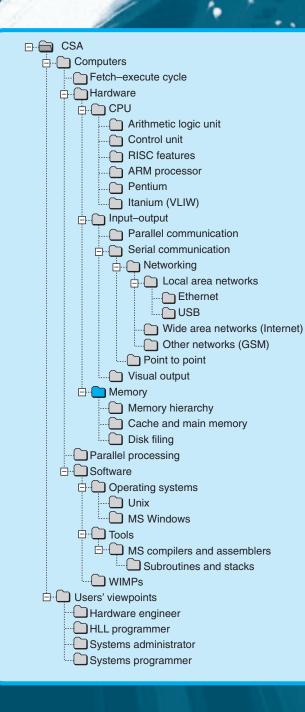

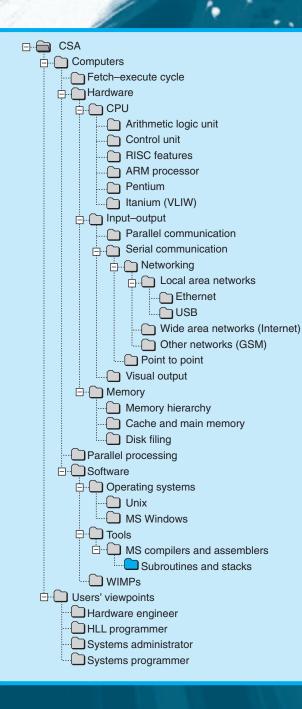

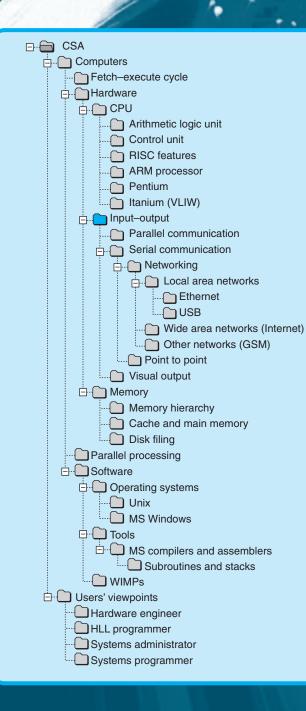

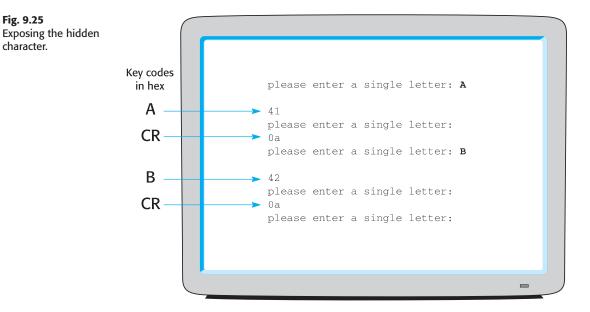

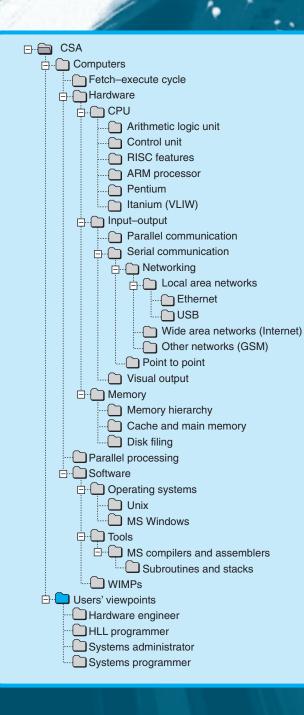

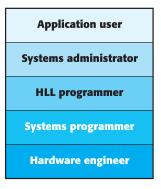

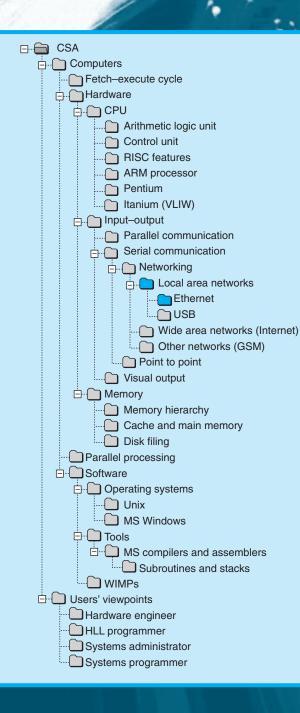

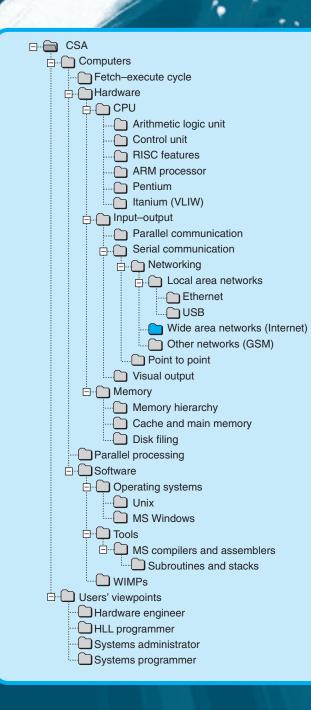

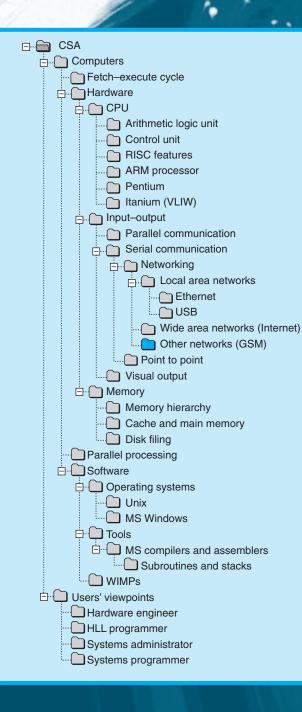

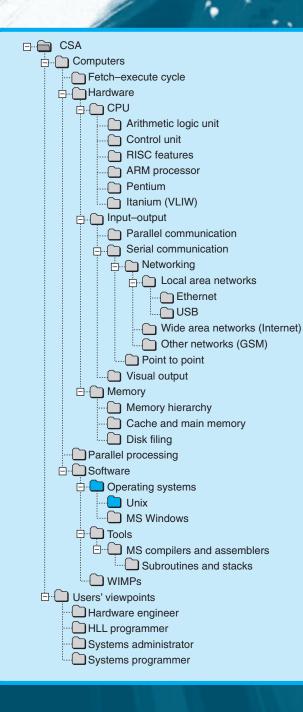

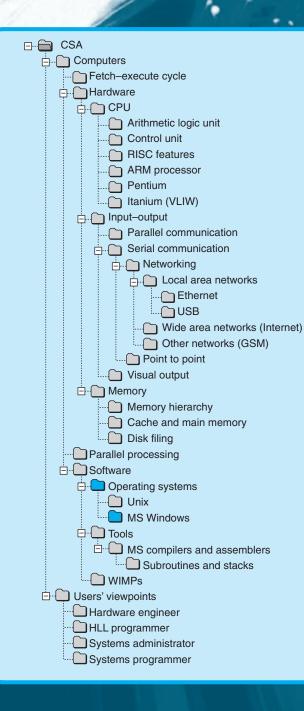

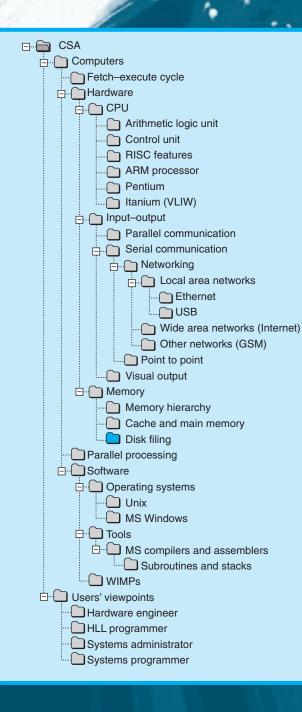

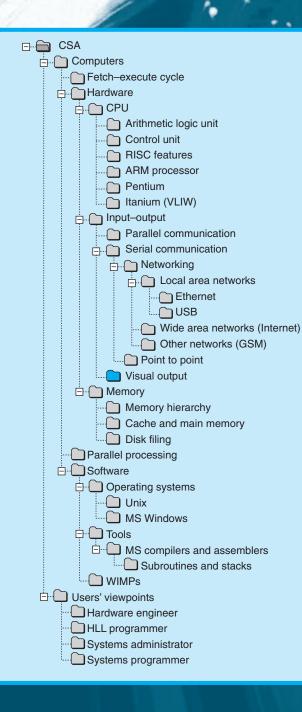

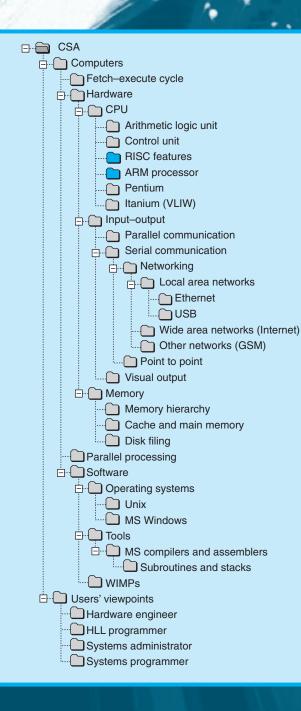

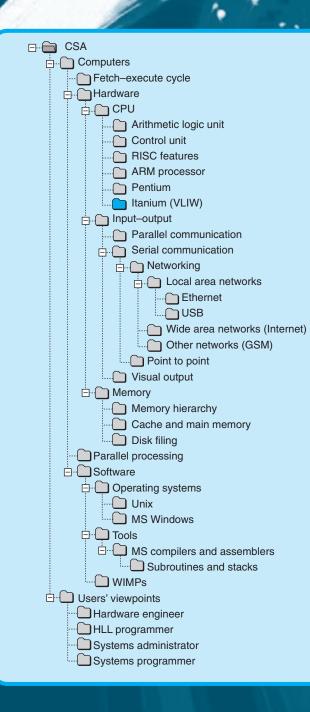

At the start of each chapter you will see a graphic representation of the contents, modelled on the familiar Windows Explorer file browser. It enables you to see the subject context of all the chapters. It is not a contents list; rather, more an ideogram. Each chapter is supplied with a small set of questions for which answers are supplied at the back of the book. It goes without saying that you should make a serious attempt to answer the questions yourself before reading the answers! A full glossary is also included at the end of the book in an attempt to deal with the appalling jargon explosion that has taken place. We all bemoan this situation, but it does constitute part of the challenge of becoming a fully blown computer professional. It cannot simply be ignored.

#### Operating systems and programming languages

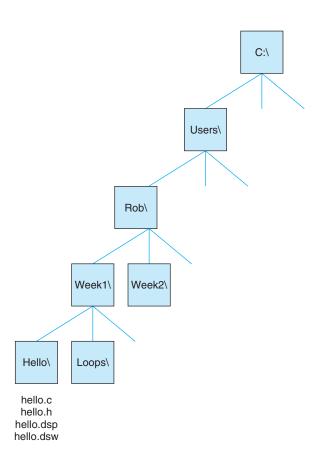

When presenting a course, or writing a text on computing, the choice of which language or operating system to use can be an emotional issue. Traditionally, university courses have tried to duck the question of commercial relevance and stick with the well-established academic favourites. I do find this frustrating, having once (twice?) tried to use Pascal for a commercial contract and then run up against all sorts of quite predictable problems which we had never honestly discussed with our students. With this experience in mind I have since always tried to use commercially viable tools in my teaching. The two operating systems that are universally seen throughout the world are Unix and Windows XP (in which we include Windows 2000). I expect you to have access to both systems for practical work. Linux is perfectly admirable for the Unix examples, although I have illustrated the text using Sun Microsystems' Solaris. As for languages, I assume that you are studying a programming language in parallel with this computer systems course, and so can quickly pick up the necessary level of C to understand my code fragments. I do not expect C++ expertise! To further assist you in testing out the examples and trying the end of chapter questions, the student edition of the Microsoft Developer Studio Visual C++ is described in this text. The Appendix contains guidance notes to help you install the package and quickly start using it. Although we will only be using it for very elementary programming examples, you can continue to progress into C++, object-oriented programming and the use of MFCs (Microsoft Foundation Classes) if you are so minded! Source code examples and a very effective online system are provided to support your learning.

#### Practical course orientation

The course that you are following may be different from ours in many aspects. I plan on a 24 week schedule, splitting the work into two semesters. In this way, each chapter serves a week of the course. The order, and to some extent the content, is determined by the practical work that is carried out in the weekly lab sessions. I believe that it is principally the practical work which fully confirms technical understanding. I could never trust a software design that had not been tested by implementation! To reduce lab sessions, or decouple them from the theoretical discussion taking place in the lectures, can weaken our ability to understand and assimilate new ideas. We all learn differently. Some like to listen, some to read, and others to do. Personally, I have always found that practical activity drives home new concepts firmly and permanently.

#### 'Listen and forget. Read and remember. Do and understand.'

#### For the tutor

#### The student readers

The typical readers that I have in mind have enrolled on a first year course in computing or a related subject area. They will be attending at least some of your weekly lectures, carrying out practical exercises, reading text books and talking to their friends about the work. They will also have regular access to the Internet, either at home or at their place of study. However, in my experience, no single one of these activities is sufficient to pass a degree course. In addition, it is unlikely that your students will only be studying computer systems and networking. In all probability there will be parallel courses in programming, systems design, mathematical methods and occasionally electronics. A successful course should help the student to integrate all these experiences and encourage cross-referencing from one discipline to another. This is precisely what this book enables them to do, since they will find links and road signs towards their other areas of study.

Our degree courses, like many, are integrated into a modular programme which offers the students some options in the second year. I find that many students require an introduction to these option subjects during the first year in order to make an informed decision. Systems administration, operating systems and networking in particular can be unknown areas for the students. This course is intended to fulfil this 'Foundation Course' function, as well as giving students a grounding in the practice and principles of computing systems.

#### Practical worksheets

I have made available on the Companion Web Site (www.pearsoned.co.uk/williams) samples of the weekly worksheets that I use with my students. These focus on aspects of the theoretical material which has just been presented in the lectures. Often a worksheet also serves as an introduction to the assessed coursework assignment which follows. As you can see, we still closely link student lab work sessions to their classroom experience, something which is not always possible within a modular programme.

#### Assessment

Because of the practical orientation of the course, I set two assessed programming assignments. In the first semester it is currently an assembler exercise using the Visual C Developer Studio. This involves accessing the PC COM port for serial communications. The second assignment is a group exercise which builds on the first. It requires the production of software to support a packet-oriented ring network, again using the PC COM port. The second programming assignment is completed in the C language, and involves protocol negotiation and cooperative working. This is intended to prepare the ground for second year courses in networking and final year courses in distributed systems. As part of the coursework assessment, I ask the students to demonstrate their code and answer a couple of questions about the structure and functionality. This does take valuable time to carry out, but in my experience is well worth the investment.

In place of a single terminal exam I prefer to set several assessed class tests. These give the student regular useful feedback, and allow for corrective action by the tutors before it is too late! The questions listed at the end of each chapter offer some preparation for the tests and benefit from summary answers provided at the end of the book. Sample test scripts are available from the publisher's secure Web site.

#### Acknowledgements

Thanks to Phil Naylor for supplying the example administration script listed in Chapter 13 and, more significantly, maintaining our network of Sun workstations so well. I must warmly thank my colleagues Bob Lang and Craig Duffy for doggedly reading the early drafts and offering helpful comments. I would also like to mention the many students, past and present, on our very special BSc Computing for Real-Time Systems degree, whose good humour and determination often brightened long debugging sessions. The best reward for any teacher is to see students progress and develop their technical confidence, leading to successful graduation and rewarding careers.

As the book grew, my wife's initial scepticism changed to benign toleration and then, as the text spread across the living room floor, to alarmed disbelief. But despite heroic proofreading and executive editorial efforts on her part, all errors are mine, and I hope you will send me your comments and views (rob.williams@uwe.ac.uk).

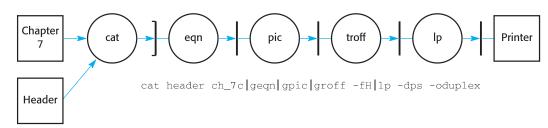

I must also give praise to Brian Kernighan for his wonderfully small pic language, which I used to draft all the line diagrams throughout the text. The original text was edited with emacs and the formatting was all carried out using groff from Richard Stallman's GNU suite. It was here that I discovered the fun of using pic to code diagrams. However, the most critical commentary was no doubt rendered by Cassie, our morose four-year-old cat, who regularly fell sound asleep straddling the monitor on which I was editing the text.

Rob Williams Department of Computing University of the West of England Bristol July 2000

The publishers would like to express their appreciation for the invaluable advice and encouragement they have received for this book from the following academics:

Hernk Corporaal Delft University, The Netherlands

Peter Hood University of Huddersfield, UK

Prasant Mohaptra Michigan State University, USA

Henk Neefs University of Gent, Belgium

Andy Pimentel University of Amsterdam, The Netherlands

Mike Scott Dublin City University

Bernard Weinberg Formerly Michigan State University, USA

#### Publisher's acknowledgements

We are grateful to the following for permission to reproduce copyright material:

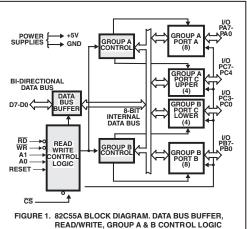

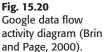

Fig. 9.2 'Datasheet (p. 3) for a Harris 82C55A, parallel port IO chip', reproduced by permission of Intersil Corporation, © Intersil Corporation; Fig. 12.3 from Hatfield, D.J. and Gerald, J. (1971) 'Program restructuring for virtual memory', *IBM Systems Journal*, Vol. 10, No. 3, p. 189, copyright 1971 by International Business Machines Corporation, reprinted with permission of the IBM Systems Journal; Figs 15.14 and 15.15 screenshot of Netscape Communicator browser window © 2005 Netscape Communications Corporation. Used with permission. Netscape Communications has not authorized, sponsored, endorsed, or approved this publication and is not responsible for its content; Fig. 15.20 and Table 15.6 from *The Anatomy of a Large-scale Hypertextual Web Search Engine* (Brin S. and Page L., 2000) by permission of Google; Fig. 21.19 with permission of IPAQ Repair and Parts, Ratby, UK; screenshots reprinted with permission from Microsoft Corporation.

In some instances we have been unable to trace the owners of copyright material, and we would appreciate any information that would enable us to do so.

# Recommended lab sessions

It is expected that the majority of the readers of this text will be students pursuing a course called Computer Science, Computing, Software Engineering, or some similar title. Such courses normally include weekly lectures and practical work in laboratories. Thus the material covered in the following chapters represents only one component of your learning experience. The following practical worksheets are available for downloading and use (from www.pearsoned.co.uk/williams), and have been planned to support and extend the principal ideas presented in each of the chapters. You may wish to read through them even if your own course demands that you carry out a different set of practical exercises.

#### Part 1

- Videos with historic interviews and equipment Search engines Web sites with information about historic computers Investigate library catalogue

- Introduction to the network Computing facilities, Unix and Windows NT Basic programmer's skills Revise binary numbers

- Inside the PC Opening up the computer Identifying parts Reviewing component names and their function

- Digital logic for the control unit Using truth tables

Drawing simple circuits

Understanding decoders

Building traffic light controllers

- Digital logic for the ALU Building a half adder Building a full adder Assembling a parallel adder/subtractor

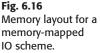

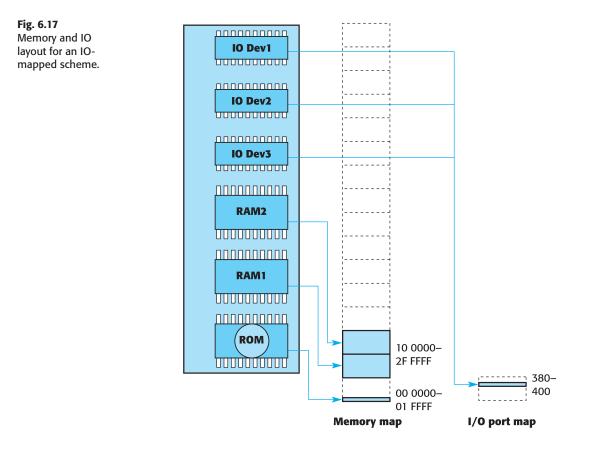

- Memory mapping Understanding the need for memory decoding Interpreting a memory map Writing a memory map from a hardware specification

- Introduction to Pentium asm Online help Setting up a project on Visual Studio Writing and compiling C programs Including asm inserts

- 8. Subroutines Calling C functions Calling asm subroutines Passing parameters Stack frame preparation and scrubbing

- Input and output methods using C routines Using the C library of IO routines Accessing COM1 and COM2 from C and asm

- Inter-computer communications using RS232 Packet data Flow control issues EOF problems

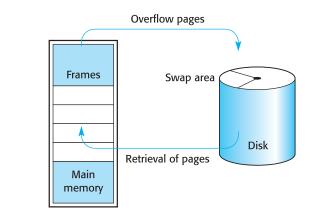

- 11. Memory performance Virtual memory swapping delays

Designing programs to run efficiently with cache

12. Assignment review

#### Part 2

- 13. The programmer's viewpoint Review last semester's practical worksheets

- 14. Accessing the LAN Ethernet cards Unix and NT network tools Looking at the arp table IP numbers DNS

- Programming with sockets

Passing data between machines

Winsock programming

Research GSM facilities.

Send email to and from a mobile handset

- Researching the Internet for information on mobile telephony Investigating GSM technology and facilities

- Introduction to operating systems Unix pipes Shell scripts

- Operating systems

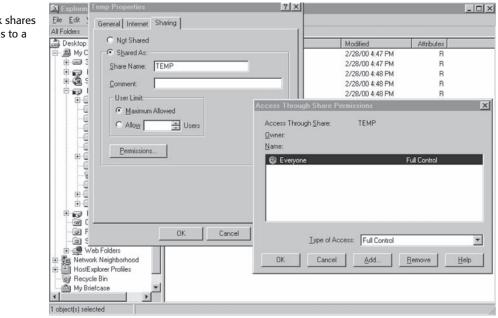

Applying XP security facilities

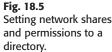

Shares and permissions

Virtual drives

- Disk Doctor

Accessing FAT boot sectors on a flash stick or floppy disk

Looking at the boot sector

Inspecting the directory and FAT

Recovering data from a damaged

FAT file system

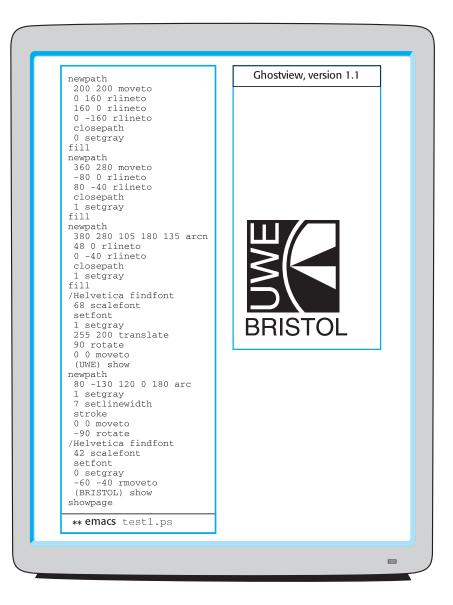

- 20. Direct PostScript programming Structure of a PostScript program Using Ghostview for previewing Inserting the header before printing Bounding box issues

- 21. Comparison of RISC and CISC Class presentations

- 22. Itanium VLIW processor

# Basic functions and facilities of a computer

| 1  | Introduction: the<br>hardware–software interfac | e 3 |

|----|-------------------------------------------------|-----|

| 2  | The von Neumann<br>Inheritance                  | 23  |

| 3  | Functional units and the fetch-execute cycle    | 47  |

| 4  | Building computers from logic: the control unit | 73  |

| 5  | Building computers from logic: the ALU          | 97  |

| 6  | Building computers from logic: the memory       | 117 |

| 7  | The Intel Pentium CPU                           | 137 |

| 8  | Subroutines                                     | 167 |

| 9  | Simple input and output                         | 185 |

| 10 | Serial communications                           | 219 |

| 11 | Parallel connections                            | 263 |

| 12 | The memory hierarchy                            | 285 |

### part 1

### Introduction: the hardware– software interface

#### Overview

If you are just starting a new course at college or university, the first week can be confusing enough without having to cope with a scary new subject. So this introductory chapter will only try to explain what areas the subject of Computer Systems covers, the relevance of networking, and why you should study it. This text focuses on the interaction of hardware and software as it affects computer performance. Because it may not be a familiar or easy topic, some reasons will be presented why you should pursue this subject in some depth. These include: the need to maintain your own PC; the advantage of keeping up with the latest developments, including interconnectivity and the Internet; appreciating your windowing interface; and being prepared for the far-reaching changes in technology which will undoubtedly arise in the future. The astonishingly successful symbiosis established between hardware and software developers shows no sign of ending.

| 1.1 | Computer systems – the importance of networking                                     | 4        |

|-----|-------------------------------------------------------------------------------------|----------|

| 1.2 | Hardware and software – mutua<br>dependence                                         | al<br>5  |

| 1.3 | Programming your way into<br>hardware – VHDL, a language fo<br>electronic engineers | or<br>6  |

| 1.4 | Systems administration – we all need to know                                        | 9        |

| 1.5 | Voice, image and data –<br>technological convergence                                | 9        |

| 1.6 | Windowing interfaces –<br>WIMPs 1                                                   | 1        |

| 1.7 |                                                                                     | 3<br>  3 |

| 1.8 | Using the PC – a case study;                                                        |          |

more reasons to study CSA

16

#### 1.1 Computer systems – the importance of networking

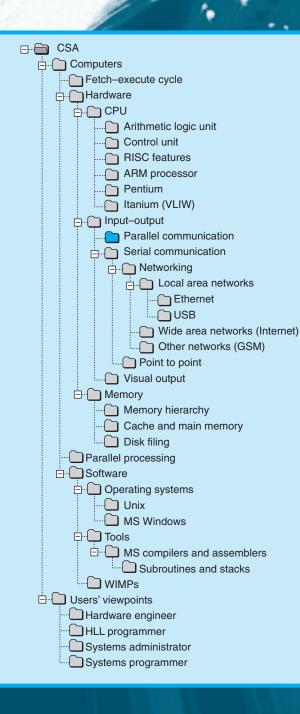

College courses often have an introductory unit called 'Computer Systems Architecture' (CSA). But because there is not yet a universal definition of CSA, quite wide latitude exists for varying curricula and divergent interpretations (Fig. 1.1). Student confusion increases because commercial terminology can be even more creative! Sometimes CSA appears in the hardware orientation of digital electronics; at other times it takes on the guise of a unified software specification for a family of computers. Rarely is the central importance of network facilities, both to the computer designer and to the end user, sufficiently acknowledged, even though we are all aware of its growing significance in society. Indeed, more and more computer science graduates become involved in the data communications industry, and would therefore benefit from a grounding in this field. Thus an aim of this text is to place networks solidly within CSA.

It is clear that computers and networks require both hardware and software in order to work. But the historical academic separation of the two poses a difficult balancing problem when presenting such a course. Both are equally important and strongly espoused by their enthusiastic supporters. The distinction between hardware and software can be likened to the distant relationship between the formal team photograph, rigidly posed in front of the goalmouth, and the exciting unpredictability of the World Cup final. The static photograph of the players only vaguely hints at the limitless possibilities of the dynamic game. With the increasing sophistication of computer hardware, perhaps it is unfortunate that the dismantling and exploration of old computers is no longer encouraged. The tumbling prices of electronic components, added to the need to have modern equipment to run the latest games, has resulted, for the moment, in a salesperson's dream. Unexpectedly, this trend, although attracting many more people to use computers, has had an adverse effect on the fundamental level of knowledge among computing undergraduates on entry to university. Although we cannot turn the clock back to the self-build hobbyist days of home

computing, knowledge of the interaction of hardware and software is still useful, if not necessary, for anyone wanting to be fully involved in the professional use of computers.

Curiosity about the computer systems which surround us, the Internet that frustrates us, and the mobile telephone networks that we increasingly rely on should drive us to investigate and question what is happening in the fields of software and electronics. The facilities that will become available to us in the next few years will depend largely on current developments in microelectronics and software design methodology. It is here that we can look for the future.

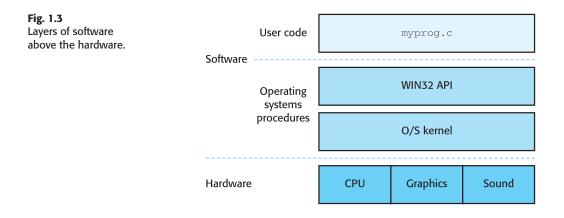

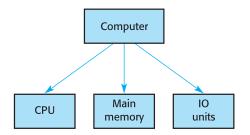

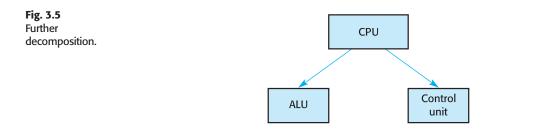

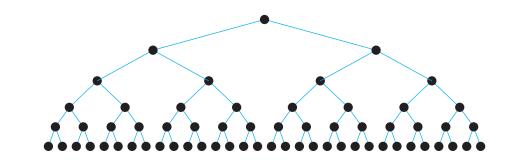

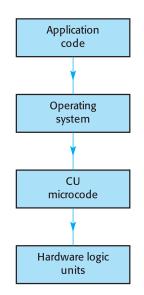

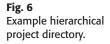

Throughout this text we will treat CSA as a study of the interaction of hardware and software which determines the performance of networked computer systems. We will also try to show that computers can always be viewed as hierarchical ordered systems which can be broken down into simpler component parts (hardware or software, as in Fig. 1.3) in order to fully understand their operation. Unlike other areas of study, such as physics or chemistry, complex ideas can always be split into simpler concepts which may then be understood more easily. This progressive decomposition approach not only is useful when studying computers, but can also be invaluable when designing and building new systems.

#### **1.2** Hardware and software – mutual dependence

Although it is widely recognized that computer systems involve both hardware and software, it is still rare for college computer courses to require you to have a comparable understanding in both fields. Perhaps the analogy of only eating half a boiled egg is appropriate – you risk missing out on the yolk (Fig. 1.2). This demarcation, or specialization, has a number of serious negative results. When teams of developers are separately recruited as hardware engineers or programmers, the danger of an antagonistic split progressively opening up between the two camps is always present. Professional rivalry can arise through simple misunderstandings due to the different approaches and vocabulary used by hardware and software engineers. Problems, when they inevitably occur, can be blamed on the other camp and then take longer to resolve. Programmers sometimes find that unsuitable equipment has already been specified without consultation, and hardware designers can sit helplessly by as unsuitable software fails to exploit the performance advantages offered by their revolutionary new circuits.