Vinu V Das Janahanlal Stephen Nessy Thankachan et al. (Eds.)

Communications in Computer and Information Science

102

# Power Electronics and Instrumentation Engineering

International Conference, PEIE 2010 Kochi, Kerala, India, September 2010 Proceedings

## Communications in Computer and Information Science 102

Vinu V Das Janahanlal Stephen Nessy Thankachan Srinivasa K. G. Hatim A. Aboalsamh Mohammad Hammoudeh Vahid Salmani Dinesh Kumar Tyagi Anjali Mohapatra Bharatheesh Jaysimha Eliathamby Ambikairajah Jon Blackledge (Eds.)

# Power Electronics and Instrumentation Engineering

International Conference, PEIE 2010 Kochi, Kerala, India, September 7-9, 2010 Proceedings

#### Main Editors

Vinu V Das

Engineers Network, Trivandrum, Kerala, India

E-mail: vinuvdas@gmail.com

Janahanlal Stephen

Mangalam College of Engineering, Ettumanoor

Kottayam, India

E-mail: drlalps@gmail.com

Nessy Thankachan

College of Engineering, Trivandrum, Kerala, India

E-mail: nessythankachan@gmail.com

Library of Congress Control Number: 2010934003

CR Subject Classification (1998): D.2, I.4, C.3, B.6, C.5.3, C.5.4

ISSN 1865-0929

ISBN-10 3-642-15738-6 Springer Berlin Heidelberg New York ISBN-13 978-3-642-15738-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

springer.com

© Springer-Verlag Berlin Heidelberg 2010 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper 06/3180 5 4 3 2 1 0

#### **Volume Editors**

#### **Editor-in-Chief**

Vinu V Das Engineers Network, India

#### **Editors**

Janahanlal Stephen Mangalam College of Engineering, Ettumanoor, Kottayam, India

Nessy Thankachan College of Engineering Trivandrum, India

#### **Associate Editors**

Srinivasa K G Hatim A Aboalsamh Mohammad Hammoudeh Vahid Salmani Dinesh Kumar Tyagi Anjali Mohapatra Bharatheesh Jaysimha Eliathamby Ambikairajah Jon Blackledge M. S. Ramaiah Institute of Technology, India King Saud University, Saudi Arabia University of Wolverhampton, UK University of California, USA BITS-Pilani, India IIIT-Bhubaneswar, India ABIBA Systems, India University of New South Wales, Australia Dublin Institute of Technology, Ireland

#### **Preface**

This book contains the best papers of the International Conference on Advances in Power Electronics and Instrumentation Engineering, PEIE 2010, organized by the Association of Computer Electronics and Electrical Engineers (ACEEE), during September 7–9, 2010 in Kochi, Kerala, India.

PEIE is an international conference integrating two major areas of electrical engineering – power electronics and instrumentation. Thus this conference reflects a continuing effort to increase the dissemination of recent research results among professionals who work in the areas of power electronics, instrumentation and electrical engineering

The program of this joint conference included several outstanding keynote lectures presented by internationally renowned distinguished researchers who are experts in the various PEIE areas. Their keynote speeches have contributed to heightening the overall quality of the program and significance of the theme of the conference.

I hope that you will find this collection of the best PEIE 2010 papers an excellent source of inspiration as well as a helpful reference for research in the aforementioned areas.

Organizing a conference like this one is not possible without the assistance and continuous support of many people and institutions. I thank Stefan Goeller, Janahanlal Stephen, R Vijay Kumar, and Nessy Thankachan for their constant support and guidance. I would like to express my gratitude to Springer's LNCS-CCIS editorial team, especially Leonie Kunz, for producing such a wonderful proceedings book.

July 2010 Vinu V Das

#### **PEIE 2010 – Organization**

#### **Technical Chair**

Hicham Elzabadani American University in Dubai, UAE

Prafulla Kumar Behera Utkal University, India

**Technical Co-chair**

Natarajan Meghanathan Jackson State University, USA

Gylson Thomas MES College of Engineering, India

**General Chair**

Janahanlal Stephen VJCET, India

Beno Benhabib University of Toronto, Canada

**Publication Chair**

R Vijaykumar NSS CE, Palakkadu, India

Brajesh Kumar Kaoushik IIT Roorke, India

**Organizing Chair**

Vinu V Das Engineers Network, India

Nessy T Electrical Machines Group, ACEEE

**Program Committee Chair**

Harry E. Ruda University of Toronto, Canada

Durga Prasad Mohapatra NIT Rourkela, India

**Program Committee Members**

Shu-Ching Chen Florida International University, USA

T.S.B. Sudarshan BITS Pilani, India

Habibollah Haro Technological University of Malaysia

Derek Molloy Dublin City University, Ireland

Jagadeesh Pujari SDM College of Engineering and Technology,

India

Nupur Giri VESIT, Mumbai, India

Animesh Adhikari Anirban Mukhopadhyay

Malabika Basu Tahseen Al-Doori

V.K. Bhat Ranjit Abraham Naomie Salim Abdullah Ibrahim

Charles McCorkell Neeraj Nehra Muhammad Nubli

Zhenyu Y Angz Keivan Navi

Rama Shankar Yadav Smriti Agrawal

Vandana Bhattacherjee R.D. Sudhaker Samuel

Amitabha Sinha Shyam Lal Debasish Jena Srinivasa K G

Bipin Bihari Jayasingh

Seyed-Hassan

Mirian-Hosseinabadi

Malay K. Pakhira Sarmistha Neogy

Sreenath Niladhuri Ananta Ojha A K Sharma

Debasis Giri Suparna Biswas S P Chowgule College, India University of Kalyani, India

Dublin Institute of Technology, Ireland American University in Dubai, UAE

SMVD University, India Armia Systems, India

Technological University of Malaysia University of Malaysia, Pahang, Malaysia

Dublin City University, Ireland SMVD University, India

University of Malaysia Pahang, Malaysia Florida International University, USA Shahid Beheshti University, Iran

MNNIT, India MNNIT, India BITS Mesra, India

S J College of Engineering, India

West Bengal University of Technology, India

Mit Moradabad, India

Biju Patnaik University of Technology, India M S Ramaiah Institute of Technology, India

CVR College of Engineering, India

Sharif University of Technology, Iran

Kalyani Government Engineering College, India

Jadavpur University, India

Podicherry Engineering College, India

ICFAI University, India

YMCA Institute of Engineering, India

IIT Kharagpur, India

WBUT, India

#### **Table of Contents**

#### Full Paper

| Novel Design for RF MEMS Capacitive Shunt Switch in K and Ku Bands                                                     | 1  |

|------------------------------------------------------------------------------------------------------------------------|----|

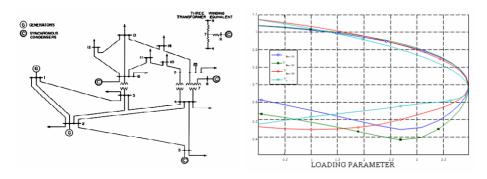

| Power System Dynamic Stability Enhancement of SMIB Using Fuzzy Logic Based Power System Stabilizer                     | 10 |

| A Novel Configuration of Unified Power Flow Controller                                                                 | 15 |

| New Results on the Global Chaos Synchronization for Liu-Chen-Liu and Lü Chaotic Systems                                | 20 |

| New Results on the Reduced Order Model Design for the Linear Discrete-Time Control Systems                             | 28 |

| Transient Stability Enhancement of a Multimachine Power System with Admittance Model Static Reactive Power Compensator | 37 |

| PEIE 2010 - Short Paper                                                                                                |    |

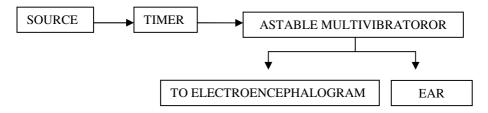

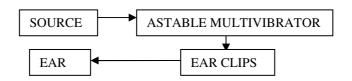

| Design of Cranial Electrotherapy Stimulator and Analyzing It with EEG                                                  | 42 |

| Analysis on Static Voltage Stability Using SVC, STATCOM, TCSC & UPFC                                                   | 46 |

| Torque Ripple Minimization of Permanent Magnet Brushless DC Motor Using Genetic Algorithm                              | 53 |

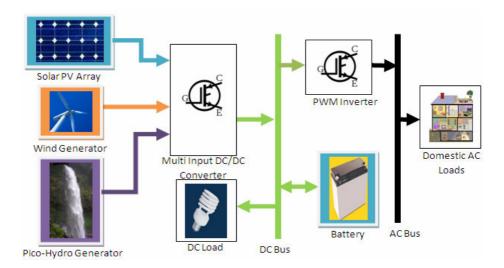

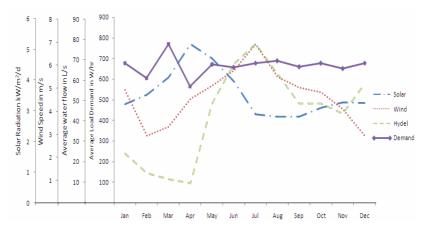

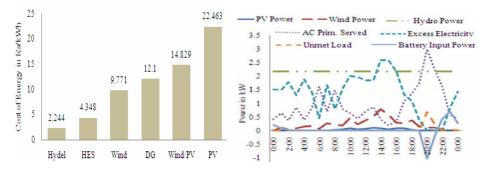

| Residential-Scale Solar/Pico-Hydel/Wind Based Hybrid Energy System for Remote Area Electrification                     | 56 |

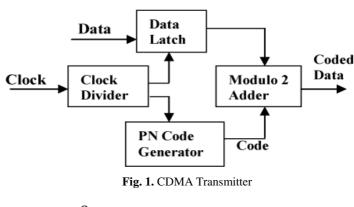

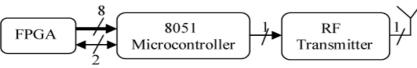

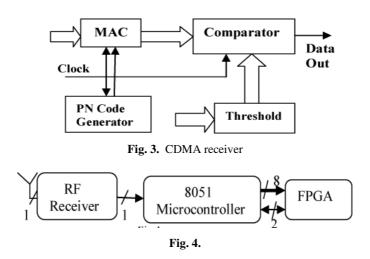

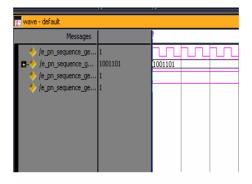

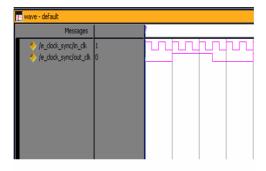

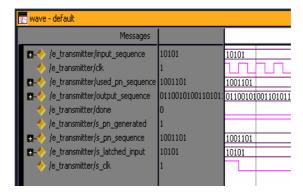

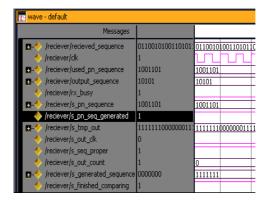

| Designing CDMA Modem in FPGA Based on DSSS                                                                                 | 63  |

|----------------------------------------------------------------------------------------------------------------------------|-----|

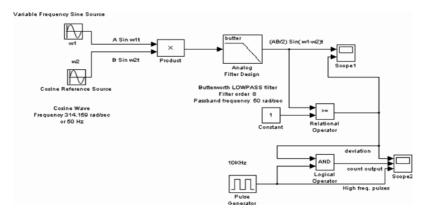

| Voltage Clamped DC-DC Converter With Reduced Reverse Recovery Current and Switch Voltage Stress                            | 69  |

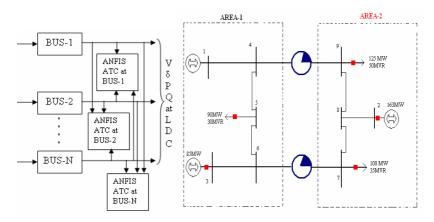

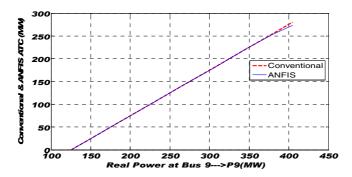

| Online Monitoring of Available Transfer Capability in Deregulated Power System Using Adaptive Neuro Fuzzy Inference System | 74  |

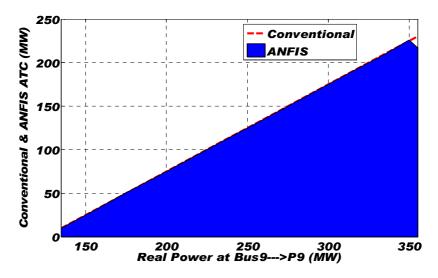

| A Novel Technique for Indication of Power Frequency Deviations in Electrical Systems                                       | 80  |

| Novel Auxiliary Switch Very-High-Frequency Zero Current Switching Resonant DC-DC Boost Converter                           | 83  |

| PEIE 2010 - Poster Paper                                                                                                   |     |

| Vulnerable Load Bus Identification Using Radial Basis Neural Network                                                       | 87  |

| FPGA Based Design of Robust Spatial Domain Image Watermarking Algorithm                                                    | 91  |

| A High Performance Direct Torque Control of PMBLDC Motor Using Hybrid (GA Based Fuzzy logic) Controller                    | 96  |

| Embedded System Design and Real Time Hardware Implementation of OLED Interface Card                                        | 100 |

| Frequency Detector Using Piezo Laminated Cantilever Beam                                                                   | 104 |

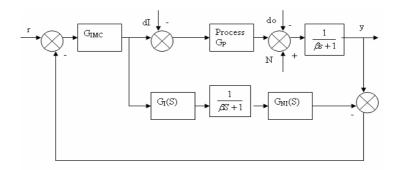

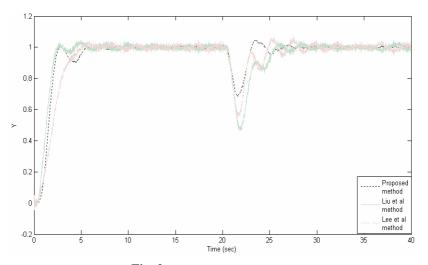

| IMC Based PID Controller Tuning for Unstable SOPDT Processes $V.K.\ Singh,\ P.K.\ Padhy,\ and\ S.K.\ Jain$                 | 108 |

| Author Index                                                                                                               | 113 |

#### Novel Design for RF MEMS Capacitive Shunt Switch in K and Ku Bands

Rakesh S. Lal, A. Amalin Prince, and Iven Jose

Department of Electrical & Electronics Engineering

BITS, Pilani – K. K. Birla Goa Campus

Zuarinagar, Goa, India

rakeshslal1989@gmail.com, amalinprince@gmail.com,

iven@bits-goa.ac.in

**Abstract.** A novel design for RF MEMS Capacitive Shunt Switch with operating bandwidth in the K and Ku bands is presented in this paper. The novel MEMS switch has got lower insertion loss than a normal switch and there is no compromise on the isolation and the operating bandwidth of the switch. The resonant frequency of the proposed switch is kept constant near 20GHz which is the midpoint of the bandwidth of the switch. A comparative study of a normal switch and the proposed switch is done. The improvement in design has been achieved by introducing discontinuities in the coplanar waveguide both in the central conductor and the ground planes. The discontinuities are represented in terms of equivalent lumped parameters. A new method of obtaining the lumped parameters of coplanar waveguide step discontinuities in the central conductor and ground planes using full wave electromagnetic simulation is also presented.

**Keywords:** MEMS, RF MEMS, Capacitive shunt switch, CPW, SAW shaped CPW, Lumped Parameter.

#### 1 Introduction

Radio Frequency Microelectromechanical Systems (RF MEMS) is gaining popularity day by day as is obvious from the vast amount of research done on this field. The field finds vast applications in space and telecommunication. Till date the most important and most researched device in RF MEMS is the switch. In comparison to contemporary state-of-the-art switching devices, MEMS switches exhibit superior electrical performance and low power consumption on a size commensurate with that of the solid state devices [1]. RF MEMS switches exhibit improvement in performance figure-of-merit and losses over conventional switches in orders of magnitude. The inevitable I-V non-linearities associated with semiconductor junctions in PIN diodes and GaAs FETs are non-existent, except for the minor hysteresis in C-V characteristics of shunt switches [1].

Capacitive shunt switches are preferred over series switches in the K and Ku bands due to their higher power handling capability [2]. Improvement in design of capacitive shunt switch was done by Wu, Q. et al. by introducing step discontinuity in the

central conductor of the CPW, resulting in better return loss and insertion loss of the switch [3]. Implementation of Distributed MEMS Transmission Line (DMTL) phase shifters using such a CPW has also been demonstrated [3-6]. But the associated disadvantage with this CPW is that the operating frequency of the switch shifts to higher values which is not desirable. The resonant frequency of the switch increases and hence the average isolation in the K and Ku bands becomes poorer than the corresponding value for the normal CPW. Hence a design is required which does not affect the frequency range of the switch and at the same time provides good average insertion loss and isolation similar to that of the SAW shaped CPW [3]. This is achieved in the switch is presented in this paper.

This paper is organized as follows. Section 2 explains the working mechanism of a Capacitive shunt switch. Section3 presents the performance comparison of the new switch with an existing capacitive shunt switch to stress upon the advantages of the new switch. Section 4 explains the extraction of lumped parameter model to model electrically the working of the proposed switch. Section 5 explains the results and finally Section 6 provides some conclusions.

#### 2 Capacitive Shunt Switch

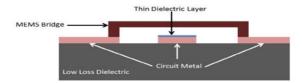

A MEMS capacitive shunt switch on CPW configuration is shown in Fig. 1. The two ends of the MEMS bridge are fixed on the ground planes of the CPW and the bridge is suspended over the transmission line.

Fig. 1. Capacitive shunt switch implemented on CPW

When the MEMS bridge is suspended above the transmission line the signal passes through without any attenuation, under ideal conditions. The switch is operated by applying a DC voltage between the bridge and the transmission line. This results in an electrostatic force between the bridge and the transmission line, causing the bridge to bend down and touch the dielectric layer on the transmission line. This results in a short circuit between the transmission line and the ground planes hence causing the RF signal to be shunted to the ground planes and hence a reflective switch results. The voltage reflection coefficient is calculated using (1).

$$\tau^2 = \frac{Z_L - Z_o}{Z_L + Z_o} \tag{1}$$

Where,  $Z_L$  = impedance of switch,  $Z_o$  = characteristic impedance of line reflection loss parameter,

$$S 11 = 10\log^2 \quad dB \tag{2}$$

transmission loss parameter,

$$S_{12} = 10 \log T^2$$

dB (3)

where,

$$T^2 = 1 - \tau^2 \tag{4}$$

The  $S_{12}$  in the ON state and OFF state of the switch is referred to as insertion loss and isolation respectively. The isolation is maximum at a particular frequency called the resonant frequency of the switch. It is given by the formula

$$f = \frac{1}{2\pi\sqrt{LC}} \text{ Hz}$$

(5)

When the DC voltage is removed, the bridge springs back to the normal position and the RF signal passes through.

#### 3 Normal CPW Configuration

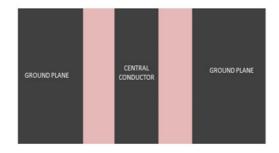

A normal CPW is shown in Fig. 2. The simulation results using Ansoft HFSS are presented.

#### 3.1 ON State

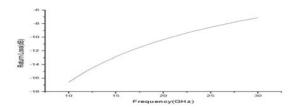

The simulation plots of the ON state scattering parameters are shown in Fig. 3 and Fig.4. The insertion losses at 12GHz, 20GHz and 27GHz are -0.18dB, -0.48dB and -0.84dB respectively. The average insertion loss in K and Ku bands combined is -0.48dB.

Fig. 2. Normal CPW (top view)

Fig. 3. Variation of ON state return loss with frequency for normal CPW

Fig. 4. Variation of insertion loss with frequency for normal CPW

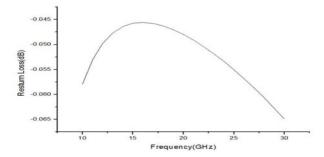

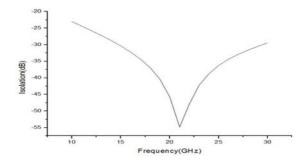

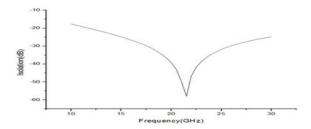

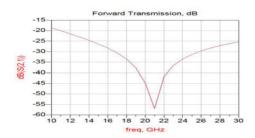

The simulation plots of the OFF state scattering parameters are shown in Fig. 5 and Fig.6. The resonant frequency is 21GHz, which is almost the mid pint of the operating frequency range, that is Ku and K bands combined. As a result, the switch by default has got good isolation, that is, isolation greater than 20dB in magnitude throughout the Ku and K bands.

Fig. 5. Variation of OFF state return loss with frequency for normal CPW

Fig. 6. Variation of isolation with frequency for normal CPW

#### 4 New CPW Configuration

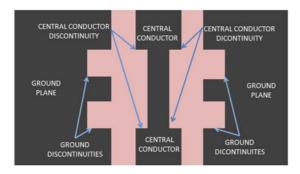

A novel CPW configuration enhancing the operating characteristics of RF MEMS Capacitive shunt switch is shown in Fig. 7. Here step discontinuities are introduced in the transmission line as well as the ground planes.

#### 4.1 ON State

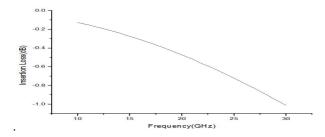

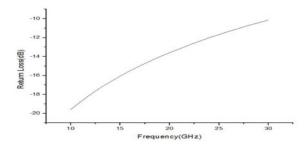

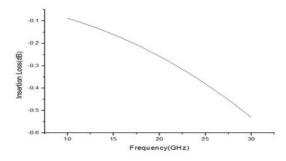

The simulation plots of the ON state scattering parameters are shown in Fig. 8 and Fig. 9. The insertion losses at 12GHz, 20GHz and 27GHz are -0.12dB, -0.25dB and -0.43dB respectively. All these values are considerably less than the corresponding values for normal CPW. The average insertion loss in the Ku and K bands combined is -0.25dB. This value is almost half the value of the normal CPW average insertion loss.

Fig. 7. CPW with central conductor and ground plane discontinuities(top view)

Fig. 8. Variation of ON state return loss with frequency for new CPW

Fig. 9. Variation of insertion loss with frequency for new CPW

#### 4.2 OFF State

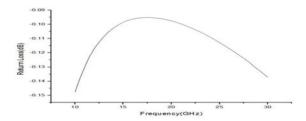

The simulation plots of the OFF state scattering parameters are shown in Fig. 10 and Fig. 11. From the isolation versus frequency plot it is clear that the resonant frequency is 21GHz which is the same as that of the normal switch. Also throughout the operating frequency of the switch the isolation is greater than 20dB. Hence there is no compromise on the isolation of the switch in case of the new CPW configuration.

Fig. 10. Variation of OFF state return loss with frequency for new CPW

Fig. 11. Variation of isolation with frequency for new CPW

#### 5 Extraction of Lumped Parameter Model

An equivalent lumped parameter modeling is done for the new CPW. The new modeling is done by analyzing the resonant frequency of the switch. The capacitance of the switch in OFF state is calculated using (5).

$$C = \frac{\varepsilon_o \varepsilon_r A}{t_d} \tag{6}$$

$\varepsilon_o$  = permittivity of vacuum,  $\varepsilon_r$  = relative permittivity of dielectric layer, A = area of overlap of switch with the transmission line,  $t_d$  = thickness of dielectric layer.

The capacitance is calculated to be 6.4pF using (6). Substituting the capacitance value in (5) the inductance is calculated to be 9.3pH. The step discontinuity in the central conductor of a CPW has been analyzed by various authors and different models have been proposed [7-9]. The different models have been tested using software simulations. The softwares used are Ansoft HFSS and Agilent ADS. Finally an equivalent circuit model consistent with the simulation results is proposed.

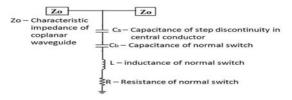

Fig. 12. Lumped Parameter model of CPW with step discontinuity in the central conductor

Simulation results of a switch implemented on a CPW with step discontinuity in central conductor, which have not been included in this paper due to space constraints, show an increase in resonant frequency of the switch to 27GHz. The increase in resonant frequency coupled with the insertion loss decrease, indicate that a new capacitance has been introduced in series with shunt impedance branch representing the switch. The added capacitance value is calculated using (1) and turns out to be 9.15pF. The lumped parameter of the switch along with the step discontinuity in central conductor is shown in Fig. 12.To confirm the validity of the equivalent model, the lumped parameter model simulation was done with Agilent ADS. The plot matches with the simulation results from HFSS hence confirming the assumption.

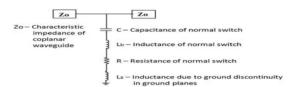

The equivalent lumped model for the ground plane discontinuities is analyzed using the same technique as presented in the above case of step discontinuity in central conductor. The capacitance of the switch is calculated using (6) and the value is 18.0pF. It is observed that the resonant frequency gets shifted to 15 GHz. The resonant frequency decrease along with the insertion loss decrease, as compared to a normal switch with resonant frequency of 21GHz, indicate that a new inductance has been introduced in series with the shunt impedance branch of the switch. The added inductance value is calculated using (5) and turns out to be 6.25pH. The lumped parameter of the switch in OFF state along with the ground discontinuity is shown in Fig. 13.

Fig. 13. Lumped Parameter model of CPW with step discontinuity in the ground planes

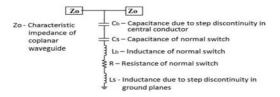

Fig. 14. Lumped Parameter of the novel switch with discontinuities in central conductor and ground planes

To confirm the validity of the equivalent circuit model, the lumped parameter model simulation was done with Agilent ADS. The plot matches with the simulation results from HFSS. The insertion loss plot of the OFF state of the switch also matches with the corresponding plot from HFSS. Hence the lumped model of the ground discontinuity shown in Fig. 13 is proved to be valid. Finally the lumped model of the CPW configuration shown in Fig. 7 is obtained as shown in Fig. 14 combining the two derived models. The isolation plot is shown in Fig. 15. It matches with the plot from HFSS shown in Fig. 11. Based on the above observations a new method is identified for extracting the equivalent circuit model for CPW step discontinuities. Step discontinuities on CPWs are of 2 types: 1) discontinuities on the central conductor, 2) discontinuities on the ground plane. As proved earlier in the case of the new CPW configuration, the discontinuities on the central conductor result in a shunt capacitance in the equivalent circuit model and discontinuities on the ground plane results in shunt inductance in the equivalent circuit model.

Based on these ideas a generalized method for extracting the equivalent circuit model of any CPW step discontinuity using full wave electromagnetic simulation is presented. Construct a MEMS capacitive shunt switch type bridge over the portion of the CPW where step discontinuities are present. The length and breadth of the switch should be such that it covers the entire region where the discontinuities are present. A dielectric layer should be placed over the central conductor and should be of the exact shape as that of the discontinuity on the central conductor. The bridge should touch the dielectric layer on the central conductor. The capacitance can be easily computed using (6).

Fig. 15. Variation of isolation with frequency for new CPW obtained from Agilent ADS

The next step is to simulate the structure on Ansoft HFSS. Extract the  $S_{12}$  parameter for a range of frequencies till the first minima is obtained. Perform simulation starting from 1GHz till a minima is found. The frequency corresponding to the minima is the resonant frequency. Substitute the value of frequency obtained from simulation and the calculated value of capacitance from (6) into (5) and obtain the value of inductance. Hence the net shunt capacitances and inductances can be determined. This method is valid for step discontinuities on both the central conductor and the ground planes of CPW.

#### 6 Results

The return loss and insertion loss for the proposed switch is found to be better in comparison to the conventional switch. The average insertion loss for normal switch

is calculated to be -0.48dB whereas for the proposed switch the value is -0.25dB, hence making a large improvement in the performance of the switch in the K and Ku bands. Moreover there is no compromise on the isolation. A unique technique to obtain the lumped parameter model without involving rigorous mathematical calculations is also presented.

#### 7 Conclusion

A novel RF MEMS capacitive shunt switch is developed for telecommunications applications. The proposed switch will find enormous application in RF MEMS phase shifters where switches with low insertion losses are required. The new method presented to obtain lumped parameter model of CPW step discontinuities can enable quick and easy analysis of CPW based devices.

#### References

- Rangra, K.J.: Electrostatic Low Actuation Voltage RF-MEMS Switches for Telecommunications. Ph.D. Dissertation, Dept. of Information and Communication Technology, University of Trento, Italy (February 2005)

- 2. Rebeiz, G.M.: RF MEMS theory, design and technique. John Wiley & Sons Inc., Hoboken (2003)

- 3. Wu, Q., Tang, K., Feng, Z.-R., Sun, F.-L., Li, L.-W.: DMTL Phase Shifter using Insulation Layer and SAW shaped CPW. In: IEEE Asia Pacific Microwave Conference (2007)

- 4. Barker, N.S., Rebeiz, G.M.: Optimization of Distributed MEMS Phase Shifters. In: IEEE MTT-S International Microwave Symposium Digest, vol. 1, pp. 3–19 (June 1999)

- Dey, S., Rangra, K.J., Shrivastava, S.J.: Design Optimization of Low Loss Distributed RF MEMS Phase Shifter. In: International Conference of Mechanical and Electronics Engineering (ICMEE), Chennai, India (2009)

- 6. Borgioli, A., Liu, Y., Nagra, A.S., York, R.A.: Low loss Distributed MEMS Phase Shifter. IEEE Microwave and Guided wave letters 10(1) (January 2000)

- Chiu, C.-W., Wu, R.-B.: Capacitance Computation for CPW Discontinuities with Finite Metallization Thickness by Hybrid Finite-Element Method. IEEE Trans. Microwave Theory Tech. 45(4), 498–504 (1997)

- 8. Chiu, C.-W.: Inductance Computation for Coplanar Waveguide Discontinuities with Finite Metallization Thickness. IEE Proc., Microwave Antennas Propag. 145(6), 496–500 (1998)

- 9. Sinclair, C., Nightingale, S.J.: An Equivalent Circuit Model for the Coplanar Waveguide Step Discontinuity. In: 1992 IEEE MTT-S International Microwave Symposium Digest, vol. 31-5, pp. 1461–1464 (June 1992)

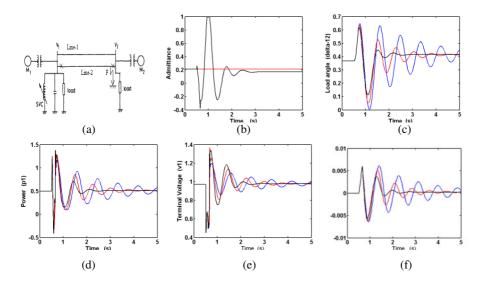

### Power System Dynamic Stability Enhancement of SMIB Using Fuzzy Logic Based Power System Stabilizer

Kamalesh Chandra Rout and P.C. Panda

Electrical Engineering Department, National Institute of Technology, Rourkela, India rout.kamalesh@gmail.com

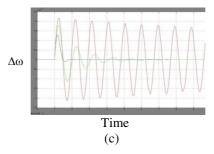

**Abstract.** The oscillations in the frequency range of 0.2 to 3.0 Hz limit the power transmission capability of a network and, sometimes, even cause a loss of synchronism and an eventual breakdown of the entire system. This paper presents an application of fuzzy logic power system stabilizer (PSS) for dynamic stability enhancement power system. Here speed deviation ( $\Delta\omega$ ) and acceleration ( $\Delta P$ ) of the rotor synchronous generator were taken as the input to the fuzzy logic controller. Depending on these variables, the inference mechanism of the fuzzy logic controller is represented by a (7 × 7) decision table i.e. 49 if-then rules. The performance of the fuzzy PSS is compared with the conventional power system stabilizer (CPSS) and without PSS. The simulations were tested under different operating conditions.

**Keywords:** Power System Stabilizer, Dynamic Stability, SMIB, Fuzzy Sets and Logic.

#### 1 Introduction

The electric power systems today are no longer operated as isolated systems, but as interconnected systems which may include thousands of electric elements and be spread over vast geographical areas. There are many advantages of interconnected power systems such as provide large amounts of power and increase reliability of the system, reduce the number of machines which are required for both operation at peak load, and required as spinning reserve to care of a sudden change of load. Stability of power system is one of the most important aspects in electric system operation. To enhance system damping, the generators are equipped with power system stabilizers (PSSs) that provide supplementary feedback stabilizing signals in the excitation systems. PSSs augment the power system stability limit and extend the power-transfer capability by enhancing the system damping of low-frequency oscillations associated with the electromechanical modes [1][2].

A System is said to be dynamically stable, if the oscillations do not acquire certain amplitude and die out quickly. Dynamic stability is concerned with small disturbances lasting for a long time. Conventional PSS (CPSS) is widely used in existing power systems and has made a contribution in enhancing power system dynamic stability. The parameters of CPSS are determined based on a linearised model of the power system around a nominal operating point where they can provide good performance. Since power systems are highly non-linear systems, with configurations and parameters that

change with time, the CPSS design based on the linearised model of the power system cannot guarantee its performance in a practical operating environment [3][4].

#### 1.1 Power System Model

The nonlinear equations of the system are:

$$\begin{split} \frac{d\delta}{dt} &= \omega_{B} S_{m} \\ \frac{dS_{m}}{dt} &= \frac{1}{2H} [-DS_{m} + T_{m} - T_{e}] \\ \frac{dE_{d}^{'}}{dt} &= \frac{1}{T_{qo}} [-E_{d}^{'} + (x_{q} - x_{q}^{'})i_{q}] \\ \frac{dE_{q}^{'}}{dt} &= \frac{1}{T_{do}} [-E_{q}^{'} + (x_{d} - x_{d}^{'})i_{d} + E_{fd}] \\ \frac{dE_{fd}}{dt} &= \frac{1}{T_{a}} [K_{a}(V_{ref} + V_{s} - V_{t}) - E_{fd}] \end{split}$$

Fig. 1. Single Machine Infinite bus system

#### 1.2 Excitation System Control Design

The specific objectives of excitation control design are:

- Maximization of the damping of the local plant mode as well as interarea mode oscillations without compromising the stability of other modes, such as the exciter mode.

- Enhancement of system transient stability.

- Prevention of adverse effects on system performance during major system upsets that cause large frequency and voltage excursions.

- Minimization of the consequences of excitation system malfunctions due to component failures.

With electric power systems, the change in electrical torque of a synchronous machine, following a small disturbance can be resolved into two components [5].

$$\Delta T_{a} = T_{S} \Delta \delta + T_{D} \Delta \omega$$

$T_{\rm s}\Delta\delta$  is the component of torque change in phase with the rotor angle deviation  $\Delta\delta$

$T_{\scriptscriptstyle D}\Delta\omega$  is the component of torque change in phase with the speed deviation  $\Delta\omega$

$T_{\rm S}$  is the synchronizing torque coefficient

$T_D$  is the damping torque coefficient

System stability depends on the existence of both components of torque.

Fig. 2. Fig. 3.

For a generator connected radially to a large power system, in the absence of automatic voltage regulator (i.e. with constant field voltage), the instability is due to the lack of sufficient synchronizing torque (i.e. -ve T<sub>S</sub>). This results in instability through a non-oscillatory mode as shown in Figure 2.

For a generator connected radially to a large power system, in the presence of automatic voltage regulator, the instability is due to the lack of sufficient damping torque (i.e. -ve  $T_D$ ). This results in instability through a oscillatory mode as shown in Figure 3.

#### 1.3 PSS Structure

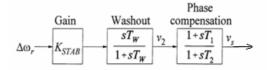

The phase compensation block provides the appropriate phase-lead characteristics to compensate for the phase-lag between the exciter input and the generator electrical torque [6]. Figure 4 shows a single 1<sup>st</sup> order block.

The signal washout block serves as a high pass filter, with the time constant  $T_w$  to allow signals associated with oscillations in  $w_r$  to pass unchanged. Without it, steady changes in speed would modify the terminal voltage. It allows the PSS to respond only to changes in speed.

The stabilizer gain K<sub>stab</sub> determines the amount of damping introduces by the PSS.

Fig. 4. PSS Structure

#### 2 Fuzzy Logic Controller

The following Figure 5. Shows the block diagram of fuzzy logic controller.

Fig. 5. Block diagram of Fuzzy Logic Controller

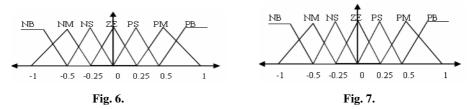

In the design of fuzzy logic controllers, unlike most conventional methods, a mathematical model is not required to describe the system under study. Here control strategy depends upon a set of rules, which describes the behavior of the controller. It generally comprises four principle components: fuzzification interface, knowledge base, decision making logic and defuzzification interface. After choosing proper variables as input and output of fuzzy controller, it is required to decide on the linguistic variables. For the power system under study, seven linguistic variables for each of the input and output variables are used to describe them. The stabilizer output is obtained by applying a particular rule expressed in the form of membership function. Figure 6 shows the membership functions for input  $\Delta\omega$  and  $\Delta P$  and Figure 7 shows the membership function for output U. Decision table in 1 shows the result of 49 rules, where a positive control signal is for the deceleration control and a negative signal is for acceleration control.

**Table 1.** Decision table of 49 rules

| speed dev. | NB | NM | NS | ZE | PS | PM | PB |

|------------|----|----|----|----|----|----|----|

| NB         | NB | NB | NB | NS | ZE | ZE | PS |

| NM         | NB | NB | NM | NS | ZE | PS | PM |

| NS         | NB | NB | NM | ZE | PS | PM | PB |

| ZE         | NB | NM | NS | ZE | PS | PM | PB |

| PS         | NB | NM | NS | ZE | PM | PB | PB |

| PM         | NM | NS | ZE | PS | PM | PB | PB |

| PB         | NS | ZE | ZE | PS | PB | PB | PB |

#### 3 Simulation Results

The test system depicted in Figure 1. is considered for analysis.

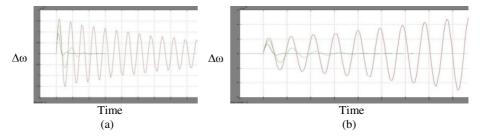

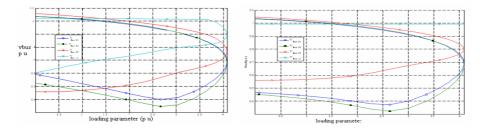

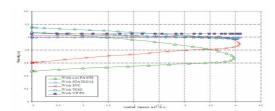

**Fig. 8.** Responses of generator when mechanical torque was changed into 0.1[pu] in 8(a) light load, 8(b) nominal load, 8(c) heavy load

Fig. 8. (continued)

#### 4 Conclusion

The target of the developed work is the damping of oscillations related to power system using fuzzy logic controller based technique on a single machine to infinite bus system. The system without stabilizer is highly oscillatory. Both the controllers are able to damp the oscillations reasonably well or to stabilize the system at most of the operating conditions. From the simulation results FuzzyPSS shows the better control performance than CPSS and no PSS power system stabilizer in terms of settling time and damping effect.

#### References

- 1. Abido, M.A.: Hybridizing Rule based Power System Stabilizers with Genetic Algorithms. IEEE Transactions on Power Systems 14, 600–607 (1999)

- Voropai, N.I., Etingov, P.V.: Application of Fuzzy Logic Power System Stabilizers to Transient Stability Improvement in a Large Electric Power System. In: IEEE PowerCon 2002, pp. 1223–1227 (October 2002)

- 3. Kundur, P., Klein, M., Rogers, G.J., Zywno, M.S.: Application of Power System Stabilizers for Enhancement of Overall Stability, vol. 4, pp. 1463–1469 (May 1989)

- 4. Hosseinzadeh, N., Kalam, A.: A Rule-Based Fuzzy Power System Stabilizer Tuned by a Neural Network. IEEE Transactions on Energy Conversion 14(3) (1999)

- Kundur, P.: Power System Control and Stability, pp. 3–168, 699–825, 1103–1166. McGraw-Hill, Inc., New York (1994)

- Larsen, R.V., Swann, D.A.: Applying Power System Stabilizers, Part I, II, III. IEEE Transactions on PAS 100(6) (June 1981)

#### A Novel Configuration of Unified Power Flow Controller

S. Baskar<sup>1</sup>, N. Kumarappan<sup>2</sup>, and R. Gnanadass<sup>3</sup>

<sup>1</sup> Assistant Professor, Dept. of EEE, Sri Manakula Vinayagar Engineering College, Puducherry, India

Tel.: +91 413 2244598, Mobile: 9443686695; Fax: +91 413 2641151

bas\_good@hotmail.com

<sup>2</sup> Professor, Dept. of EEE, Annamalai University, India

kumarappan\_n@yahoo.com

<sup>3</sup> Associate Professor, Dept. of EEE, Pondicherry Engineering College, India

gnanadass@yahoo.com

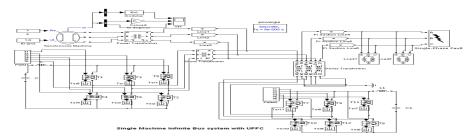

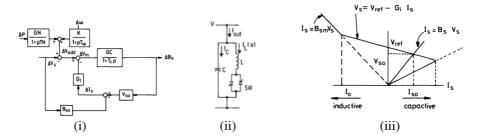

Abstract. This paper presents the modeling and design of Unified Power Flow Controller (UPFC) using novel control technique in the inverter. The proposed control technique implements the 150 degree conduction mode of individual IGBTs in the inverter. The UPFC can be operated using PWM controllers to enhance the reactive power compensating and regulating the line voltage and also reduces the harmonic in the transmission line current and voltage. The 150 degree inverter is advantageous and increases the RMS values of output voltages, when compared to 120° mode, and 180° mode. Total required VA rating of the inverters is reduced greatly over wide load conditions. The operating performance of UPFC is demonstrated on Single Machine Infinite Bus (SMIB) system for different case studies. The proposed model considerably improves the system stability by damping the oscillation during the vulnerable conditions.

**Keywords:** SMIB, Switching Level Modeling, 150 degree inverter, Unified Power Flow Controller.

#### 1 Introduction

In recent years, new types of FACTS devices have been investigated that may be used to increase power system operation flexibility and controllability, to enhance system stability and to achieve better utilization of existing power systems. The evolution in power electronic devices along with the development and control have allowed the design and implementation of structural controllers known as Flexible AC Transmission System (FACTS), which are emerging as feasible technology for the improvement of system's dynamic behavior. The benefits arising from FACTS devices are widely appreciated. The concept of Flexible AC Transmission System (FACTS) was introduced [1,2] as a family of power electronic equipments which have emerged for controlling and optimizing flow of electrical power in the transmission line. The concepts of Unified Power Flow Controller (UPFC) its performance and steady state characteristics have been widely reported in the literature [3,4]. The UPFC has been researched broadly and many research articles dealing with UPFC modeling, analysis, control and application have been published in the recent

years. Mathematical models were developed for UPFC to determine steady state operational characteristics using state space equations without considering the effects of converters and the dynamics of generator [5, 6]. The performance of UPFC was analyzed by designing a series converter using conventional and advanced controllers [7, 8]. Mathematical model of UPFC using general PWM and space vector approach was used to perform the power flow studies, Eigen analysis and transient stability investigations [9]. A non linear dynamic small signal model of network with UPFC was established for transient studies. The model evaluated the compensation effects of UPFC, optimized the location of UPFC and its control design [10]. An equivalent two bus power network was developed based on sets of equations for a system including the UPFC was proposed. This provided a useful tool to rate; evaluate the performance of UPFC on power systems [11].

The UPFC was modeled as voltage source model and PWM switching level model. The voltage source model of UPFC was constructed with equivalent voltage source and impedances using MATLAB. The switching level model of UPFC was designed and simulated in EMTP. The equivalent impedance of voltage source model was found from the dynamic responses of UPFC switching level model. The results show that switching level model was more accurate than voltage source model [12]. The optimal location and equivalent impedance of UPFC are found by voltage source model and switching level model by varying the amplitude and phase angle of injected voltage [13]. In laboratory implementation of FACTS devices, UPFC was setup by PWM modulation controllers which provides more effective control of real and reactive power flow [14].

The new configuration of UPFC has proposed. Two inverters are connected face to face on AC side instead of back to back through a common DC link. It greatly reduces the VA rating of the inverters [15]. The new conduction mode of 120° inverter is implemented in the brushless DC motor and the performances are analyzed [16]. The conduction mode of 150° implemented and it is analyzed for three phase inverter performance [17]. The double band hysteresis current controller was designed for STATCOM to compensate the reactive power in the distribution network. The current error and switching frequency are reduced [18]. Hence in this paper, the proposed technique aims at to control the real and reactive power flow in the transmission lines, by implementing the 150° conduction angle for individual switches in the inverters.

In this paper dynamic control UPFC is analyzed with six pulse converter using switching level model. The architecture of the paper in Section 2 explains the conduction mode of inverter, section 3 describes the modeling of UPFC, and section 4 provides the simulation results. The conclusion is summarized in Section 5.

#### 2 New Conduction Mode of Voltage Source Inverter (VSI)

In this  $150^{\circ}$  conduction mode of inverter topology twelve switching patterns are presented per cycle with each pattern duration is  $30^{\circ}$ . Three transistors conduct in one interval, while only two transistors conduct in the next one. The gating signals are shifted from each other by  $60^{\circ}$  to get three phase balanced voltages. A  $30^{\circ}$  dead-time period is provided between the firing of each two series-switches in each leg. The firing pulse waveform for IGBT as shown in Fig.1.

While comparing with  $180^\circ$  and  $120^\circ$  degree mode the advantage is to increases the RMS values of output voltages. It provides a  $30^\circ$  safety margin period, which is large enough, to avoid short circuit on the dc supply. It Produces seven level phase-voltage waveforms,  $(0, \pm V_d/3, \pm V_d/2, \pm 2V_d/3)$ , Compared to only four or three levels in  $180^\circ$  and  $120^\circ$  modes, respectively. It highly reduces the total harmonic distortion (THD) and DF of output voltage waveforms, by presenting 12-step waveforms, which are closer to the sinusoidal waveform compared to the original 6-step ones. The implementation of  $150^\circ$  inverter almost eliminates the low order harmonics that has 1/n of fundamental magnitude in previous mode, by improving the 1/n undesired magnitude relation.

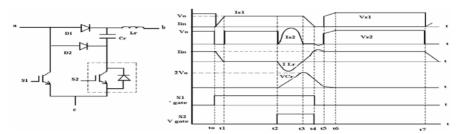

Fig. 1. Firing pulse of 150° conduction mode

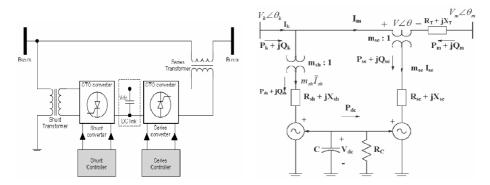

#### 3 Modeling of UPFC

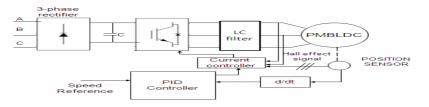

In SMIB model the synchronous generator is connected to the linear load through the Power transformer and " $\pi$ " section model of transmission line. The UPFC is located at the middle of the transmission line. The shunt and series device of UPFC consists of three phase IGBT converter with PWM controller. The shunt converter is connected to the transmission line in parallel through a three phase transformer. The series converter is connected to the transmission line in series through the three single phase transformer.

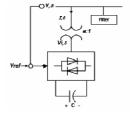

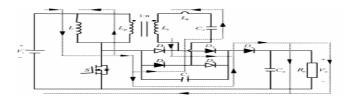

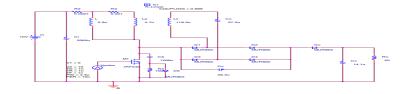

This modeling is done with Simulink blockset and simulation is carried out in MATLAB environment as shown in Fig.2.

Fig. 2. Switching level model of Unified Power Flow Controller (UPFC)

#### 4 Simulation Results

#### CASE (I)

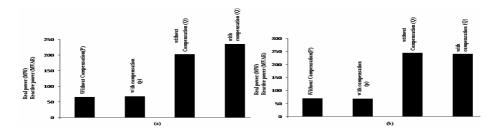

In this case, the SMIB is connected with 75% and 125% base load condition. The real and reactive power tracings are obtained through simulation and their magnitudes

different load conditions are given in Fig.3 (a) & (b). After the insertion of UPFC, the power tracings are obtained with constant modulation index.

Fig. 3. Real and Reactive Power Flow before and after compensation (a) load 1 (b) load 2

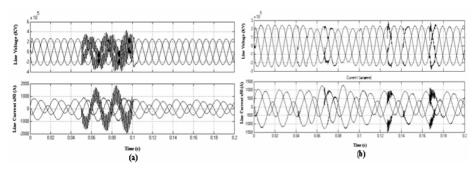

#### CASE (II)

To illustrate the performance of UPFC in the transient conditions, a transmission single phase to ground fault is created at load end of the SMIB system. The fault is cleared at 0.1 seconds. The variation of line voltage and current before and after inserting the UPFC is obtained to illustrate its impact. The corresponding voltage and current wave forms are given in the Figures 4(a) & (b). The simulation results shows that after inserting the UPFC the voltage and current oscillations are very much reduced. It reaches its initial value quickly. The UPFC will produce stable state within half of the time in the fundamental frequency.

Fig. 4. Line voltage & line current during fault condition (a) before connecting UPFC (b) after connecting UPFC

#### 5 Conclusion

In this paper, 150° conduction mode of three phase inverter is designed and implemented in Unified Power Flow Controller and the performance are analyzed. The simulation model is simulated using MATLAB/SIMULINK environment. These switching schemes have been implemented in the developed UPFC model & the performance is demonstrated on SMIB system with linear loads. This controller improves the performance of dynamic stability and transient stability and achieves good damping of power and voltage oscillations in the system.

#### References

- [1] Hingorani, N.G.: Understanding FACTS-Concepts and Technology of Flexible AC Transmission Systems. In: IEEE Power Engineering society. Standard publishers, IEEE press (2001)

- [2] Song, Y.H., Johns, A.T.: Flexible ac transmission systems FACTS. IEE, London (1999)

- [3] Gyugi, L.: Unified Power-Flow Control Concept for Flexible AC Transmission Systems. Proceedings of IEE-C 139, 323–331 (1992)

- [4] Gyugi, L., et al.: The Unified Power Flow Controller: A new approach to power transmission control. IEEE Trans. Power Delivery 10(2), 1085–1097 (1995)

- [5] Papic, I.: Mathematical analysis of FACTS devices based on a voltage source converter, Part 1: mathematical models. Electric Power Systems Research 56, 139–148 (2000)

- [6] Papic, I.: Mathematical analysis of FACTS devices based on a voltage source converter, Part II: steady state operational characteristics. Electric Power Systems Research 56, 149–157 (2000)

- [7] Round, S.D., Yu, Q., Norum, L.E., Undeland, T.M.: Performance of a Unified power flow controller using A D-Q control system. In: AC and DC power transmission Conference Pub. No. 423. IEEE, Los Alamitos (1996)

- [8] Yu, Q., Round, S.D., Norum, L.E., Undeland, T.M.: Dynamic control of UPFC, pp. 508–514. IEEE, Los Alamitos (1996)

- [9] Nabavi-Niaki, A., Iravani, M.R.: Steady state dynamic model on UPFC. IEEE Trans. Power Systems 11(4) (1996)

- [10] Smith, K.S., Ran, L., Penman, J.: Dynamic modeling of a unified power flow controller. IEE Proc. Gener. Transm. Distrib. 144(1) (1997)

- [11] Keri, A.J.F., Lombard, X., Edris, A.A.: UPFC: Modeling and Analysis. IEEE Trans. on power Delivery 14(2) (1999)

- [12] Won, D.-J., Chung, I., Moon, S.-I.: Determination of equivalent impedances of UPFC voltage-source model from the dynamic responses of UPFC switching-level model. Electric power systems 25, 463–470 (2003)

- [13] Rajeswari, S., Gnanadass, R., Venkatesh, P.: Modeling of Unified power flow controller for active power Regulation. In: Institution of engineers, Calcutta, India, vol. 90, pp. 33– 39 (2009)

- [14] Dong, L., Crow, M.L., Yang, Z., Shen, C., Zhang, L., Atcitty, S.: A Reconfigurable FACTS system for University Laboratories. IEEE Trans. power systems 19(1), 120–128 (2004)

- [15] Wang, J., Peng, F.Z.: A Novel Configuration of Unified Power Flow Controller. In: 18th IEEE power electronics Conference and exposition, vol. 2, pp. 919–924 (2003)

- [16] Sudhoff, S.D., Krause, P.C.: Operating Modes of the Brushless DC Motor with a 120 Degree Inverter. IEEE transaction on Energy Conversion 5(3) (September 1990)

- [17] Saied, M.H., Mostafa, M.Z., Abdel-Moneim, T.M., Yousef, H.A.: On Three Phase Six-Switches Voltage Source Inverter: A 150° Conduction Mode. Member IEEE, Alexandria Univercity (2006)

- [18] Kim, B.S., Oh, W.H., Shin, E.C., Seo, S.J., Lee, S.B., Yoo, J.Y.: Current Control Method using a Double Band Hysteresis. In: IEEE conference, Busan, Korea (2004)

#### New Results on the Global Chaos Synchronization for Liu-Chen-Liu and Lü Chaotic Systems

Sundarapandian Vaidyanathan<sup>1</sup> and Suresh Rasappan<sup>2</sup>

Vel Tech Dr. RR & Dr. SR Technical University, Avadi-Vel Tech Road, Avadi, Chennai-600 062, Tamil Nadu, India Tel.: +91-44-26841622; Fax: +91-44-26840605 sundarvtu@gmail.com

**Abstract.** This paper investigates the global chaos synchronization of two identical Liu-Chen-Liu chaotic systems (2007) and two different chaotic systems, namely, Liu-Chen-Liu chaotic system (2007) and Lü chaotic system (2002). Nonlinear control is an effective method for making two identical chaotic systems or two different chaotic systems synchronized. Since the Lyapunov exponents are not required for the calculations, this method is an effective and convenient to synchronize two identical and different chaotic systems. Numerical simulations are also given to validate the proposed synchronization approach.

#### 1 Introduction

Chaos synchronization is an important topic in the nonlinear control systems. Synchronization of chaotic systems is an active research problem developed and studied extensively in the last few decades ([1]-[17]). The idea of synchronizing two identical chaotic systems was first introduced by Carroll and Pecora ([1]-[2]). Synchronization has been widely explored in a variety of fields including physical [3], chemical [4], ecological [5] systems, secure communications ([6]-[8]) etc.

In most of the synchronization approaches, the master-slave or drive-response formalism is used. If a particular chaotic system is called the master or drive system and another chaotic system is called the slave or response system, then the idea of synchronization is to use the output of the master system to control the response of the slave system so that the slave system tracks the output of the master system asymptotically. Since the seminal work by Carroll and Pecora [1], a variety of impressive approaches have been proposed for the synchronization of chaotic systems such as PC method ([1]-[2]), sampled-data feedback synchronization method [9], OGY method [10], time-delay feedback approach [11], backstepping design method [12], adaptive design method ([13]-14]), sliding mode control method [15], etc.

This paper is organized as follows. In Section 2, the methodology of chaotic synchronization by nonlinear control method is given. In Section 3, the chaos synchronization of two identical Liu-Chen-Liu chaotic systems is discussed. In Section 4, the chaos synchronization of Liu-Chen-Liu and Lü chaotic systems is discussed. Section 5 gives the conclusions of this paper.

#### 2 Problem Statement and Methodology

Consider the chaotic system described by the dynamics

$$\dot{x} = Ax + f(x) \tag{1}$$

where  $x \in \mathbb{R}^n$  is the state of the system, A is the  $n \times n$  matrix of the system parameters and  $f: \mathbb{R}^n \to \mathbb{R}^n$  is the nonlinear part of the system. The system (1) is considered as the *master* or *drive* system. Also, the chaotic system described by the dynamics

$$\dot{y} = By + g(y) + u \tag{2}$$

is considered the *slave* or *response* system, where  $y \in R^n$  is the state vector of the slave system, B is the  $n \times n$  matrix of the system parameters,  $g: R^n \to R^n$  is the nonlinear part of the slave system and  $u \in R^n$  is the nonlinear controller of the slave system. If A = B and f = g, then x and y are the states of two identical chaotic systems. If  $A \neq B$  and  $f \neq g$ , then x and y are the states of two different chaotic systems. The global chaos synchronization problem is to design a controller which synchronizes the states of the master system (1) and the slave system (2) for all initial conditions x(0),  $y(0) \in R^n$ . The synchronization error is defined as

$$e = y - x \tag{3}$$

Then the synchronization error dynamics is obtained as

$$\dot{e} = By - Ax + g(y) - f(x) + u \tag{4}$$

Thus, the global synchronization problem is essentially to find a controller u so as to stabilize the error dynamics (4) for all initial conditions  $e(0) \in R^n$ , i.e.  $\lim_{t \to \infty} \|e(t)\| = 0$  for all initial conditions  $e(0) \in R^n$ .

This paper uses Lyapunov function methodology for the synchronization of master system (1) and slave system (2). By the Lyapunov function methodology, a candidate Lyapunov function is taken as

$$V(e) = e^T P e. (5)$$

where P is a  $n \times n$  positive definite matrix. Note that  $V: \mathbb{R}^n \to \mathbb{R}^n$  is a positive definite function by construction. It is assumed that the parameters of the master and slave systems are known and that the states of both systems (1) and (2) are measurable. If a controller u can be found such that

$$\dot{V}(e) = -e^T Q e, \tag{6}$$

where Q is a positive definite matrix, then  $\dot{V}: \mathbb{R}^n \to \mathbb{R}^n$  is a negative definite function. Hence, by Lyapunov stability theory [20], the error dynamics (4) is globally exponentially stable and hence the condition (5) will be satisfied for all initial conditions

$e(0) \in \mathbb{R}^n$ . Then the states of the master system (1) and the slave system (2) are globally exponentially synchronized.

#### 3 Synchronization of Two Identical Liu-Chen Liu Systems

In this section, the nonlinear control method is applied for the synchronization of two identical Liu-Chen-Liu chaotic systems [18]. The Liu-Chen-Liu system (2007) is taken as the master system, which is described by the equations

$$\dot{x}_1 = a(x_2 - x_1)

\dot{x}_2 = bx_1 + kx_1x_3

\dot{x}_3 = -cx_3 - hx_1x_2$$

(7)

where a,b,c,h and k are positive real constants. The Liu-Chen-Liu system (2007) is also taken as the slave system, which is described by the equations

$$\dot{y}_1 = a(y_2 - y_1) + u_1

\dot{y}_2 = by_1 + ky_1y_3 + u_2

\dot{y}_3 = -cy_3 - hy_1y_2 + u_3$$

(8)

where  $u = [u_1, u_2, u_3]^T$  is the nonlinear controller to be designed so as to synchronize the states of the identical Liu-Chen-Liu systems (8) and (9).

The synchronization error is defined by

$$e_1 = y_1 - x_1, \ e_2 = y_2 - x_2, \ e_3 = y_3 - x_3$$

(9)

The error dynamics is obtained as

$$\dot{e}_1 = a(e_2 - e_1) + u_1

\dot{e}_2 = be_1 + k(y_1 y_3 - x_1 x_3) + u_2

\dot{e}_3 = -ce_3 - h(y_1 y_2 - x_1 x_2) + u_3$$

(10)

The candidate Lyapunov function is taken as

$$V(e) = \frac{1}{2}e^{T}e = \frac{1}{2}\left(e_{1}^{2} + e_{2}^{2} + e_{3}^{2}\right)$$

(11)

A simple calculation gives

$$\dot{V}(e) = ae_1(e_2 - e_1) + e_1u_1 + be_1e_2 + ke_2(y_1y_3 - x_1x_3) + e_2u_2 - ce_3^2 - he_3(y_1y_2 - x_1x_2) + e_3u_3$$

(12)

We choose

$$u_{1} = -(a+b)e_{2}$$

$$u_{2} = -e_{2} + k(x_{1}x_{3} - y_{1}y_{3})$$

$$u_{3} = h(y_{1}y_{2} - x_{1}x_{2})$$

(13)

Substitution of (13) into (12) yields

$$\dot{V}(e) = -ae_1^2 - e_2^2 - ce_3^2 \tag{14}$$

which is a negative definite function on  $R^3$  since a,c>0. Hence, by Lyapunov stability theory [20], then the error dynamics (13) is globally exponentially stable. Thus, we have proved the following result.

**Theorem 1.** The identical Liu-Chen-Liu chaotic systems (7) and (8) are exponentially and globally synchronized for any initial conditions with the nonlinear controller u defined by (13).

#### **Numerical Results**

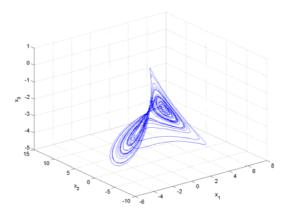

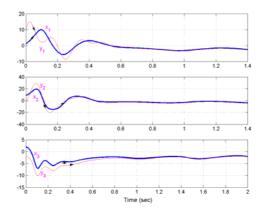

Fig. 1. Chaotic Portrait of the Liu-Chen-Liu System

For the numerical simulations, the fourth-order Runge-Kutta method is used to solve the system using MATLAB. For the Liu-Chen-Liu chaotic system (7), the parameter values are taken as those which result in chaotic behaviour of the system. When a=10, b=40, c=2.5, h=1 and k=16, the Liu-Chen-Liu system (7) has a reversed butterfly-shaped attractor as shown in Figure 1.

The initial values of the master system (7) are taken as  $x_1(0) = 1$ ,  $x_2(0) = 9$  and  $x_3(0) = 2$ , while the initial values of the slave system (8) are taken as  $y_1(0) = 9$ ,  $y_2(0) = -3$  and  $y_3(0) = -2$ . Figure 2 shows that the synchronization between the states of the master system (7) and the slave system (8) occur in 2 seconds.

Fig. 2. Synchronization of the Identical Liu-Chen-Liu Systems

## 4 Synchronization of Liu- Chen-Liu and Lu Chaotic Systems

In this section, the nonlinear control method is applied for the synchronization of two different chaotic systems described by Lü system [19] as the *master* or *drive* system and the Liu-Chen-Liu system [18] as the *slave* or *response* system. The dynamics of the Lü system, taken as the master system, is described by

$$\dot{x}_1 = \alpha(x_2 - x_1)

\dot{x}_2 = \gamma x_2 - x_1 x_3

\dot{x}_3 = x_1 x_2 - \beta x_3$$

(15)

where  $\alpha, \beta$  and  $\gamma$  are positive constants.

The dynamics of the Liu-Chen-Liu system, taken as the slave system, is described by

$$\dot{y}_1 = a(y_2 - y_1) + u_1

\dot{y}_2 = by_1 + ky_1y_3 + u_2

\dot{y}_3 = -cy_3 - hy_1y_2 + u_3$$

(16)

where a, b, c, h, k are positive constants and  $u = [u_1, u_2, u_3]^T$  is the nonlinear controller to be designed so as to synchronize the states of the different chaotic systems (15) and (16). The synchronization error is defined by

$$e_1 = y_1 - x_1, \ e_2 = y_2 - x_2, \ e_3 = y_3 - x_3$$

(17)

The error dynamics is obtained as

$$\dot{e}_{1} = a(y_{2} - y_{1}) - \alpha(x_{2} - x_{1}) + u_{1}

\dot{e}_{2} = by_{1} - \gamma x_{2} + ky_{1}y_{3} + x_{1}x_{3} + u_{2}

\dot{e}_{3} = -cy_{3} + \beta x_{3} - hy_{1}y_{2} - x_{1}x_{2} + u_{3}$$

(18)

The candidate Lyapunov function is taken as

$$V(e) = \frac{1}{2}e^{T}e = \frac{1}{2}\left(e_1^2 + e_2^2 + e_3^2\right)$$

(19)

A simple calculation gives

$$\dot{V}(e) = ae_1(y_2 - y_1) - \alpha e_1(x_2 - x_1) + e_1 u_1 + be_2 y_1 - \gamma e_2 x_2 + e_2(ky_1 y_3 + x_1 x_3) + e_2 u_2 - ce_3 y_3 + \beta e_3 x_3 - e_3(hy_1 y_2 + x_1 x_2) + e_3 u_3$$

(20)

We choose

$$u_{1} = (\alpha - a)(x_{2} - x_{1}) - (a + b)e_{2}$$

$$u_{2} = -e_{2} - bx_{1} + \gamma x_{2} - ky_{1}y_{3} - x_{1}x_{3}$$

$$u_{3} = (c - \beta)x_{3} + hy_{1}y_{2} + x_{1}x_{2}$$

(21)

Substitution of (21) into (20) yields

$$\dot{V}(e) = -ae_1^2 - e_2^2 - ce_3^2 \tag{22}$$

which is a negative definite function on  $R^3$  since a, c > 0. Hence, by Lyapunov stability theory [20], then the error dynamics (18) is globally exponentially stable.

Thus, we have proved the following result.

**Theorem 2.** The Lü chaotic system (15) and the Liu-Chen-Liu chaotic system (16) are exponentially and globally synchronized for any initial conditions with the nonlinear controller u defined by (21).

#### **Numerical Results**

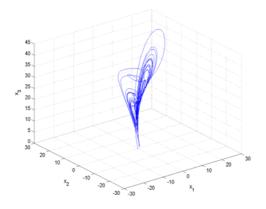

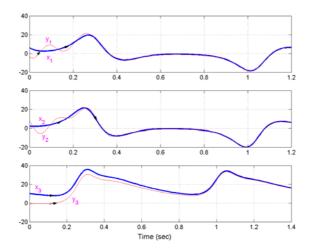

For the numerical simulations, the fourth-order Runge-Kutta method is used to solve the system using MATLAB. For the Lü chaotic system (15), the parameter values are taken as those which result in chaotic behavior of the system. When  $\alpha = 36$ ,  $\beta = 3$  and  $\gamma = 20$ , the Lü system (15) has chaotic behavior as shown in Figure 3.

Fig. 3. Chaotic Portrait for Lü System

Fig. 4. Synchronization of Liu-Chen-Liu and Lü Chaotic Systems

The initial values of the master system (15) are taken as  $x_1(0) = 6$ ,  $x_2(0) = 2$  and  $x_3(0) = 10$ , while the initial values of the slave system (16) are taken as  $y_1(0) = -3$ ,  $y_2(0) = 8$  and  $y_3(0) = -1$ . Figure 4 shows that the synchronization between the states of the master system (15) and the slave system (16) occur in 1.2 seconds.

#### 5 Conclusions

In this paper, nonlinear control method based on Lyapunov stability theory is proposed to synchronize two identical chaotic systems, namely Liu-Chen-Liu chaotic system (2007) and two different chaotic systems, namely Lü system (2002) and Liu-Chen-Liu chaotic system (2007). Numerical simulations are also given to validate the proposed synchronization approach for the global synchronization of chaotic systems. Since the Lyapunov exponents are not required for the calculation, the proposed nonlinear control method is effective and convenient to synchronize chaotic systems.

#### References

- [1] Carroll, T.L., Pecora, L.M.: Synchronization in chaotic systems. Phys. Rev. Lett. 64, 821–824 (1990)

- [2] Carroll, T.L., Pecora, L.M.: Synchronizing chaotic circuits. IEEE Trans. Circ. Sys. 38, 453–456 (1991)

- [3] Lakshmanan, M., Murali, K.: Chaos in Nonlinear Oscillators: Controlling and Synchronization. World Scientific, Singapore (1996)

- [4] Han, S.K., Kerrer, C., Kuramoto, Y.: Dephasing and bursting in coupled neural oscillators. Phys. Rev. Lett. 75, 3190–3193 (1995)

- [5] Blasius, B., Huppert, A., Stone, L.: Complex dynamics and phase synchronization in spatially extended ecological system. Nature 399, 354–359 (1999)

- [6] Murali, K., Lakshmanan, M.: Secure communication using a compound signal from generalized synchronizable chaotic systems. Physics Letters A 241, 303–310 (1998)

- [7] Cuomo, K.M., Oppenheim, A.V.: Circuit implementation of synchronized chaos with application to communication. Phys. Rev. Lett. 71, 65–68 (1993)

- [8] Kocarev, L., Parlitz, U.: General approach for chaotic synchronization with application to communication. Phys. Rev. Lett. 74, 5028–5031 (1995)

- [9] Lu, J.A., Xie, J., Lu, J., Chen, S.H.: Control chaos in transition system using sampled-data feedback. Applied Mathematics and Mechanics 24, 1309–1315 (2006)

- [10] Ott, E., Grebogi, C., Yorke, J.A.: Controlling chaos. Phys. Rev. Lett. 64, 1196–1199 (1990)

- [11] Lu, J., Wu, X., Han, X., Lu, J.: Adaptive feedback synchronization of a unified chaotic system. Phys. Lett. A 329, 327–333 (2004)

- [12] Park, J.H., Kwon, O.M.: A novel criterion for delayed feedback control of time-delay chaotic systems. Chaos, Solitons and Fractals 17, 709–716 (2003)

- [13] Wu, X., Lu, J.: Parameter identification and backstepping control of uncertain Lu system. Chaos, Solitons and Fractals 18, 721–729 (2003)

- [14] Yu, Y.G., Zhang, S.C.: Adaptive backstepping synchronization of uncertain chaotic systems. Chaos, Solitons and Fractals 27, 1369–1375 (2006)

- [15] Yau, H.T.: Design of adaptive sliding mode controller for chaos synchronization with uncertainties. Chaos, Solitons and Fractals 22, 341–347 (2004)

- [16] Agiza, H.N., Yassen, M.T.: Synchronization of Rösssler and Chen dynamical systems using active control. Phys. Lett. A 278, 191–197 (2001)

- [17] Liu, L., Chen, S.Y., Liu, C.X.: Experimental confirmation of a new reversed butterfly-shaped attractor. Chin. Phys. 16, 1897–1900 (2007)

- [18] Lü, J., Chen, G.: A new chaotic attractor coined. International Journal on Bifurcation and Chaos 12, 659–661 (2002)

## New Results on the Reduced Order Model Design for the Linear Discrete-Time Control Systems

V. Sundarapandian<sup>1</sup>, M. Kavitha<sup>2</sup>, and C.S. Ravichandran<sup>3</sup>

Vel Tech Dr. RR & Dr. SR Technical University, Avadi-Vel Tech Road, Avadi, Chennai-600 062, Tamil Nadu, India

Tel.: +91-44-26841622; Fax: +91-44-26840605

sundarvtu@gmail.com

<sup>2</sup> Vel Tech Dr. RR & Dr. SR Technical University, Avadi-Vel Tech Road, Avadi, Chennai-600 062, Tamil Nadu, India

Tel.: +91-44-26841622; Fax: +91-44-26840605

<sup>3</sup> Department of Computer Science and Engineering, SSK College of Engineering, Coimbatore, Tamil Nadu, India

**Abstract.** In this paper, we obtain the reduced order model for the linear discrete-time control systems using the dominant state of the control systems. Using the reduced order model, we derive necessary and sufficient conditions for the observer design of linear discrete-time control systems. Our method essentially uses the model reduction of the original linear control systems.

#### 1 Introduction

During the past four decades, a significant attention has been paid to the construction of reduced-order observers and stabilization using reduced-order controllers for linear control systems [1-7]. The standard observer design for linear systems either estimates the full state vector or a linear functional of the state vector as originally proposed by Luenberger [1]. As far as the stabilization of linear control systems is concerned, the state vector may not be available for measurement and so when the linear control system is both controllable and observable, we use the separation principle for linear control systems and use an estimate of the state in lieu of the state vector. This approach works well with small-scale linear systems. However, for large-scale linear systems, the order of the observer is comparable with the order of the observed state dynamics. As a consequence, the observer design problem for large-scale linear control systems involves potential numerical and practical difficulties, and so the state feedback control laws using an estimate of the state in lieu of the state vector may not yield the desired stabilization results.

In this paper, we derive a reduced-order model for any linear discrete-time control system and our approach is based on the approach of using the dominant state of the given linear discrete-time control system, *i.e.* we derive the reduced-order model for a given linear discrete-time control system keeping only the dominant state of the given linear plant. The dominant state of a linear control system corresponds to the *slow modes* of the linear system, while the non-dominant state of the control system corresponds to the *fast modes* of the linear system [4-5, 7-10].

As an application of our recent work [9], we first derive the reduced-order model of the given linear discrete-time control system. Using the reduced-order model obtained, we characterize the existence of a reduced-order exponential observer that tracks the state of the reduced-order model, i.e. the dominant state of the original linear plant. We note that the model reduction and the reduced-order observer design detailed in this paper are discrete-time analogs of the results of Aldeen and Trinh [7] for the observer design of the dominant state of continuous-time linear control systems.

This paper is organized as follows. In Section 2, we derive the reduced-order plant of a given linear discrete-time control system. In Section 3, we derive necessary and sufficient conditions for the exponential observer design for the reduced-order linear control plant. In Section 4, we present an example to illustrate the main results of this paper, viz. deriving the reduced order model for a linear discrete-time plant. In Section 5, we summarize the results obtained in this paper.

### 2 Reduced Model for the Linear System

Consider a linear discrete-time control system  $S_1$  given by

$$x(k+1) = A x(k) + B u(k)$$

$$y(k) = C x(k)$$

(1)

where  $x \in \mathbb{R}^n$  is the *state*,  $y \in \mathbb{R}^p$  the *output* and  $u \in \mathbb{R}^m$  the *input* of the linear control system (1). First, we suppose that we have performed an identification of the *dominant* and *non-dominant states* of the given linear control system using the *modal approach* as described in [9]. Without loss of generality, we may assume that

$$x = \begin{bmatrix} x_1 \\ x_2 \end{bmatrix}$$

where  $x_1 \in R^r$  represents the *dominant* state and  $x_2 \in R^{n-r}$  represents the *non-dominant* state. Then the system (1) takes the form

$$\begin{bmatrix} x_1(k+1) \\ x_2(k+1) \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \begin{bmatrix} x_1(k) \\ x_2(k) \end{bmatrix} + \begin{bmatrix} B_1 \\ B_2 \end{bmatrix} u(k)$$

$$y(k) = \begin{bmatrix} C_1 & C_2 \end{bmatrix} \begin{bmatrix} x_1(k) \\ x_2(k) \end{bmatrix}$$

(2)

From (2), we have

$$x_{1}(k+1) = A_{11} x_{1}(k) + A_{12} x_{2}(k) + B_{1} u(k)$$

$$x_{2}(k+1) = A_{21} x_{1}(k) + A_{22} x_{2}(k) + B_{2} u(k)$$

$$y(k) = C_{1} x_{1}(k) + C_{2} x_{2}(k)$$

(3)

For the sake of simplicity, we will assume that the matrix A has distinct eigenvalues. We note that this condition is usually satisfied in most practical situations. Then it follows that A is diagonalizable. Thus, we can find a nonsingular matrix P consisting of the n independent eigenvectors of A so that

$$P^{-1}AP = \Lambda$$

where  $\Lambda$  is a diagonal matrix consisting of the n eigenvalues of A. We introduce new coordinates on the state space given by

$$\xi = P^{-1}x\tag{4}$$

Then the plant takes the form

$$\xi(k+1) = \Lambda \, \xi(k) + P^{-1}B \, u(k)$$

$$y(k) = CP \, \xi(k)$$

Thus, we have

$$\begin{bmatrix} \xi_{1}(k+1) \\ \xi_{2}(k+1) \end{bmatrix} = \begin{bmatrix} \Lambda_{1} & 0 \\ 0 & \Lambda_{2} \end{bmatrix} \begin{bmatrix} \xi_{1}(k) \\ \xi_{2}(k) \end{bmatrix} + P^{-1}Bu(k)$$

$$y(k) = C P \begin{bmatrix} \xi_{1}(k) \\ \xi_{2}(k) \end{bmatrix}$$

(5)

where  $\Lambda_1$  and  $\Lambda_2$  are  $r \times r$  and  $(n-r) \times (n-r)$  diagonal matrices respectively.

Define matrices  $\Gamma_1$ ,  $\Gamma_2$ ,  $\Psi_1$  and  $\Psi_2$  by

$$P^{-1}B = \begin{bmatrix} \Gamma_1 \\ \Gamma_2 \end{bmatrix} \text{ and } CP = \begin{bmatrix} \Psi_1 & \Psi_2 \end{bmatrix}$$

(6)

where  $\Gamma_1 \in \mathbb{R}^{r \times m}$ ,  $\Gamma_2 \in \mathbb{R}^{(n-r) \times m}$ ,  $\Psi_1 \in \mathbb{R}^{p \times r}$  and  $\Psi_2 \in \mathbb{R}^{p \times (n-r)}$ .

From (5) and (6), we see that the plant (3) has the following simple form in the new coordinates (4):

$$\xi_{1}(k+1) = \Lambda_{1} \xi_{1}(k) + \Gamma_{1} u(k)$$

$$\xi_{2}(k+1) = \Lambda_{2} \xi_{2}(k) + \Gamma_{2} u(k)$$

$$y(k) = \Psi_{1} \xi_{1}(k) + \Psi_{2} \xi_{2}(k)$$

(7)

Next, we make the following assumptions:

- (H1) As  $k\to\infty$ ,  $\xi_2(k+1)\approx\xi_2(k)$ , i.e.  $\xi_2$  takes a constant value in the steady-state.

- **(H2)** The matrix  $I \Lambda_2$  is invertible.

Then it follows from (7) that for large values of k, we have

$$\xi_2(k) \approx \Lambda_2 \, \xi_2(k) + \Gamma_2 \, u(k)$$

i.e.

$$\xi_2(k) \approx \left(I - \Lambda_2\right)^{-1} \Gamma_2 \, u(k) \tag{8}$$

Substituting (8) into (7), we get the reduced-order model in the  $\xi$  -coordinates as

$$\xi_{1}(k+1) = \Lambda_{1} \xi_{1}(k) + \Gamma_{1} u(k)$$

$$y(k) = \Psi_{1} \xi_{1}(k) + \Psi_{2}(I - \Lambda_{2})^{-1} \Gamma_{2} u(k)$$

(9)

We note that (9) represents the reduced-order model of the plant in the new coordinates. To obtain the reduced-order model of the plant in its original coordinates, we proceed as follows. Set

$$P^{-1} = Q = \begin{bmatrix} Q_{11} & Q_{12} \\ Q_{21} & Q_{22} \end{bmatrix}$$

where  $Q_{11} \in R^{r \times r}$ ,  $Q_{12} \in R^{r \times (n-r)}$ ,  $Q_{21} \in R^{(n-r) \times r}$  and  $Q_{22} \in R^{(n-r) \times (n-r)}$ . By the linear change of coordinates (4), it follows that  $\xi = P^{-1}x = Q$  x. Thus, we have

$$\begin{bmatrix} \xi_1(k) \\ \xi_2(k) \end{bmatrix} = Q \begin{bmatrix} x_1(k) \\ x_2(k) \end{bmatrix} = \begin{bmatrix} Q_{11} & Q_{12} \\ Q_{21} & Q_{22} \end{bmatrix} \begin{bmatrix} x_1(k) \\ x_2(k) \end{bmatrix}.$$

Hence, it follows that

$$\xi_1(k) = Q_{11} x_1(k) + Q_{12} x_2(k)$$

$$\xi_2(k) = Q_{21} x_1(k) + Q_{22} x_2(k)$$

(10)

Using(8)and(10), we get

$$\xi_{2}(k) = Q_{21} x_{1}(k) + Q_{22} x_{2}(k) \approx (I - \Lambda_{2})^{-1} \Gamma_{2} u(k). \tag{11}$$

Next, we make the following assumption.

**(H3)** The matrix  $Q_{22}$  is invertible.

Using (H3), the equation (11) may be simplified as

$$x_2(k) \approx -Q_{22}^{-1} Q_{21} x_1(k) + Q_{22}^{-1} (I - \Lambda_2)^{-1} \Gamma_2 u(k).$$

(12)

To simplify the notation, we define matrices

$$R = -Q_{22}^{-1} Q_{21} \text{ and } S = Q_{22}^{-1} (I - \Lambda_2)^{-1} \Gamma_2$$

(13)

Using (13), the equation (12) may be simplified as

$$x_2(k) \approx R \ x_1(k) + S \ u(k).$$

(14)

Substituting (14) into (13), we obtain the **reduced-order model**  $S_2$  of the given plant  $S_1$  in its original coordinates as

$$x_{1}(k+1) = A_{1}^{*} x_{1}(k) + B_{1}^{*} u(k)$$

$$y(k) = C_{1}^{*} x_{1}(k) + D_{1}^{*} u(k)$$

(15)

where the matrices  $A_1^*$ ,  $B_1^*$ ,  $C_1^*$  and  $D_1^*$  are defined by

$$A_{1}^{*} = A_{11} + A_{12}R$$

$$B_{1}^{*} = B_{1} + A_{12}S$$

$$C_{1}^{*} = C_{1} + C_{2}R$$

$$D_{1}^{*} = C_{2}S$$

(16)

### 3 Reduced Order Observer Design

In this section, we state and prove an important result that prescribes a simple, practical procedure for estimating the dominant-state of the given linear control system that satisfies the assumptions (H1)--(H3).

**Theorem 1.** Let  $S_1$  be the linear system described by

$$x(k+1) = A x(k) + B u(k)$$

$$y(k) = C x(k)$$

(17)

Under the assumptions (H1)-(H3), the reduced-order model  $S_2$  of the plant  $S_1$  can be obtained [see Section 2] as

$$x_{1}(k+1) = A_{1}^{*} x_{1}(k) + B_{1}^{*} u(k)$$

$$y(k) = C_{1}^{*} x_{1}(k) + D_{1}^{*} u(k)$$

(18)

where  $A_1^*$ ,  $B_1^*$ ,  $C_1^*$  and  $D_1^*$  are defined as in (16). To estimate the dominant state of the system  $\mathcal{S}_1$ , consider the candidate observer  $\mathcal{S}_3$  defined by

$$z_{1}(k+1) = A_{1}^{*}z_{1}(k) + B_{1}^{*}u(k) + K_{1}^{*}[y(k) - C_{1}^{*}z_{1}(k) - D_{1}^{*}u(k)]$$

(19)

Define the estimation error as  $e = z_1 - x_1$ . Then  $e(k) \to 0$  as  $k \to \infty$  if and only if the matrix  $K_1^*$  is such that the matrix  $A_1^* - K_1^*C_1^*$  is convergent (note that a square matrix E is defined to be convergent if and only if all the eigenvalues of E

lie inside the open unit disc of the complex plane). If  $(C_1^*, A_1^*)$  is observable, then we can construct an observer of the form (19) having any desired speed of convergence.

*Proof.* From (3), we have

$$x_1(k+1) = A_{11} x_1(k) + A_{12} x_2(k) + B_1 u(k).$$

(20)

Adding and subtracting  $(A_{12} - K_1^* C_2) R x_1(k)$  in the R.H.S. of (20), we get

$$x_{1}(k+1) = (A_{11} + A_{12}R - K_{1}^{*} C_{2} R) x_{1}(k) - (A_{12} - K_{1}^{*}C_{2}) R x_{1}(k) + A_{12} x_{2}(k) + B_{1} u(k)$$

(21)

Subtracting (21) from (20), and simplifying using the definitions (16), we have

$$e(k+1) = (A_1^* - K_1^* C_1^*) e(k) - (A_{12} - K_1^* C_2) [x_2(k) - R x_1(k) - S u(k)].$$

(21)

The assumptions (H1)-(H3) yield  $x_2(k) \approx R x_1(k) + S u(k)$ .

Therefore,  $e(k+1) \approx (A_1^* - K_1^* C_1^*) e(k)$ . Hence, it follows that

$$e(k) \approx \left(A_1^* - K_1^* C_1^*\right)^k e(0).$$

(22)

From (23), it is immediate that  $e(k) \to 0$  as  $k \to \infty$  for all values of e(0) if and only if all the eigenvalues of the matrix  $A_1^* - K_1^* C_1^*$  lie inside the open unit disc of the complex plane. This completes the proof.

## 4 Numerical Example

Consider the fourth order discrete-time control system  $\,S_1\,$  described by

$$x(k+1) = A x(k) + B u(k)$$

$$y(k) = C x(k)$$

(23)

where

$$A = \begin{bmatrix} 0.8940 & -0.4237 & -0.0083 & 0.0001 \\ 0.4237 & 0.8735 & -0.0296 & 0.0003 \\ -0.0083 & 0.0296 & 0.2328 & 0.0433 \\ -0.0001 & 0.0003 & -0.0433 & 0.1485 \end{bmatrix}$$

$$B = \begin{bmatrix} -0.4214 & 0.4474 & -0.2296 & -0.0025 \end{bmatrix}^{T},$$

$$C = \begin{bmatrix} -0.4214 & -0.4474 & -0.2296 & 0.0025 \end{bmatrix}.$$

eigenvalues of A are:  $\lambda_{1,2} = 0.8835 \pm 0.4241i$ ,  $\lambda_{3,4} = 0.1909 \pm 0.0089i$ .

The dominance measure of the eigenvalues is calculated as in [9] and obtained as

$$\Omega = \begin{bmatrix} 15.5459 & 15.5459 & 0.0214 & 0.0214 \\ 15.5578 & 15.5578 & 0.0202 & 0.0202 \\ 0.6105 & 0.6105 & 0.7652 & 0.7652 \\ 0.0263 & 0.0263 & 0.7652 & 0.7652 \end{bmatrix}$$

To determine the dominance of the k <sup>th</sup> eigenvalue in all the n states, we use the measure (see [9]),  $\Theta_k = \sum_{i=1}^n \Omega_{ik}$ . Thus, we obtain

$$\Theta = \begin{bmatrix} 31.7405 & 31.7405 & 1.5720 & 1.5720 \end{bmatrix}$$

To determine the relative dominance of the  $k^{\text{th}}$  eigen value in the  $i^{\text{th}}$  state, we use the measure (see [9]),  $\phi_{ik} = \left| \frac{\Omega_{ik}}{\Theta_k} \right| \times 100$ . Thus, we obtain

$$\Phi = \begin{bmatrix} 48.9781 & 48.9781 & 1.3613 & 1.3613 \\ 49.0156 & 49.0156 & 1.2850 & 1.2850 \\ 1.9234 & 1.9234 & 48.6768 & 48.6768 \\ 0.0829 & 0.0829 & 48.6768 & 48.6768 \end{bmatrix}$$

Thus, it is easy to see that the first two states  $x_1, x_2$  are the dominant states and the last two states  $x_3, x_4$  are the non-dominant states. To find the reduced order model of the plant (24), we first represent the plant (33) in the phase variable form as

$$A = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ -0.0351 & 0.4313 & -1.6716 & 2.1488 \end{bmatrix},$$

$$B = \begin{bmatrix} 0 & 0 & 0 & 1 \end{bmatrix}^T$$

,  $C = \begin{bmatrix} -0.0021 & 0.0035 & 0.0835 & 0.0302 \end{bmatrix}$ .

The reduced order model of this plant using the construction detailed in Section II is obtained as

$$X_{1}(k+1) = A_{1}^{*}X_{1}(k) + B_{1}^{*}u(k)$$

$$y(k) = C_{1}^{*}X_{1}(k) + D_{1}^{*}u(k)$$

where

$$A_{1}^{*} = \begin{bmatrix} 0 & 1.0000 \\ -0.9604 & 1.7670 \end{bmatrix}, B_{1}^{*} = \begin{bmatrix} 0 \\ 1.5275 \end{bmatrix}$$

$$C_{1}^{*} = \begin{bmatrix} -0.1335 & 0.2163 \end{bmatrix} \text{ and } D_{1}^{*} = \begin{bmatrix} 0.2551 \end{bmatrix}.$$

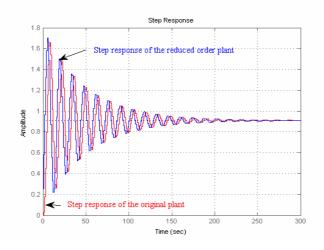

The step responses of the original plant and the reduced order plant are plotted in Figure 1, which validates the reduced-order model obtained for the given plant

Fig. 1. Step Responses of the Original and Reduced Plants

It is also easy to check that the observability matrix is